# Development of Data Acquisition and Detector Controller Electronics for the Low Energy X-Ray Detector of the Simbol-X Space Mission

Diplomarbeit

eingereicht von Henry Sebastian Grasshorn Gebhardt

Eberhard Karls Universität Tübingen Fakultät für Mathematik und Physik Kepler Center for Astro and Particle Physics Institut für Astronomie und Astrophysik Abteilung Astronomie

November 2009

# Contents

| D  | eutsc | he Zu  | sammenfassung                    | 7  |

|----|-------|--------|----------------------------------|----|

| Pı | refac | е      |                                  | 9  |

| 1  | X-r   | ay Em  | ission in the Universe           | 11 |

|    | 1.1   | Emiss  | ion Mechanisms                   | 11 |

|    |       | 1.1.1  | Blackbody Radiation              | 11 |

|    |       | 1.1.2  | Inverse Compton Scattering       | 12 |

|    |       | 1.1.3  | Synchrotron Radiation            | 12 |

|    |       | 1.1.4  | Bremsstrahlung                   | 13 |

|    |       | 1.1.5  | Emission and Absorption Lines    | 13 |

|    | 1.2   | Astro  | nomical Sources of X-rays        | 13 |

|    |       | 1.2.1  | Active Galactic Nuclei           | 13 |

|    |       | 1.2.2  | Cosmic X-ray Background          | 15 |

|    |       | 1.2.3  | X-ray Binaries                   | 15 |

|    |       | 1.2.4  | Supernova Remnants               | 16 |

|    |       | 1.2.5  | Intracluster Gas                 | 16 |

| 2  | The   | e Simb | ol-X Mission                     | 19 |

|    | 2.1   | The R  | Lise of Astronomical Instruments | 19 |

|    | 2.2   | Previo | ous X-Ray Missions               | 20 |

|    | 2.3   | Simbo  |                                  | 21 |

|    |       | 2.3.1  | Wolter Optics                    | 21 |

|    |       | 2.3.2  | X-ray Detector System            | 22 |

| 3 | The | Interf  | ace Controller                     | <b>27</b> |

|---|-----|---------|------------------------------------|-----------|

|   | 3.1 | Interfa | ce Controller Requirements         | 27        |

|   | 3.2 | Genera  | l IFC Design Considerations        | 29        |

|   |     | 3.2.1   | Equality                           | 30        |

|   |     | 3.2.2   | Uniqueness                         | 30        |

|   |     | 3.2.3   | Simplicity                         | 31        |

|   |     | 3.2.4   | Beauty                             | 31        |

|   | 3.3 | IFC co  | mponents                           | 32        |

|   |     | 3.3.1   | SpaceWire core                     | 32        |

|   |     | 3.3.2   | Receiver                           | 33        |

|   |     | 3.3.3   | Sender                             | 34        |

|   |     | 3.3.4   | $ADC\_control$                     | 34        |

|   |     | 3.3.5   | SEQ_control                        | 35        |

|   |     | 3.3.6   | EPP_control                        | 36        |

|   |     | 3.3.7   | PWR_control                        | 37        |

|   | 3.4 | Additio | onal components for testing        | 37        |

|   |     | 3.4.1   | EPP data simulator                 | 38        |

|   |     | 3.4.2   | ECH_control                        | 39        |

|   |     | 3.4.3   | SIN_control                        | 39        |

|   | 3.5 | Summa   | ary                                | 39        |

| 4 | The | Space   | Wire Protocol                      | 41        |

|   | 4.1 | SpaceV  | Vire Basics                        | 41        |

|   |     | 4.1.1   | Basic Signals and Connectors       | 42        |

|   |     | 4.1.2   | Low Voltage Differential Signaling | 43        |

|   |     | 4.1.3   | Data Strobe Encoding               | 43        |

|   |     | 4.1.4   | Characters and Control Codes       | 45        |

|   |     | 4.1.5   | The Parity Bit                     | 45        |

|   |     | 4.1.6   | Packets                            | 46        |

|   | 4.2 | Establi | shing a SpaceWire Link             | 47        |

|   |     | 4.2.1   | Flow Control                       | 49        |

4

|    |       | 4.2.2  | The Run State                                          | 49        |

|----|-------|--------|--------------------------------------------------------|-----------|

|    |       | 4.2.3  | Link-Level Error Notification: The Exchange of Silence | 50        |

|    | 4.3   | Applic | ation Side Interface                                   | 51        |

|    | 4.4   | Conclu | usion                                                  | 51        |

| 5  | The   | Space  | Wire-to-USB Converter SWitty                           | <b>53</b> |

|    | 5.1   | Test S | etup with a SpaceWire PCI Card                         | 53        |

|    | 5.2   | Space  | Wire interfacing teletype                              | 55        |

|    |       | 5.2.1  | Software Interface and Features                        | 55        |

|    |       | 5.2.2  | The Universal Serial Bus                               | 56        |

|    |       | 5.2.3  | SWitty Design                                          | 58        |

|    |       | 5.2.4  | SpaceWire Character 8-bit Encoding                     | 60        |

|    | 5.3   | Conclu | usion                                                  | 61        |

| С  | onclu | sion a | nd Outlook                                             | 63        |

| B  | bliog | raphy  |                                                        | 66        |

| ום | bilog | ларпу  |                                                        | 00        |

| Α  | The   | Unive  | ersal Serial Bus                                       | 67        |

|    | A.1   | USB I  | Basics                                                 | 67        |

|    |       | A.1.1  | Topology                                               | 68        |

|    |       | A.1.2  | Physical Layer                                         | 69        |

|    |       | A.1.3  | USB 2.0 Transceiver Macrocell Interface                | 70        |

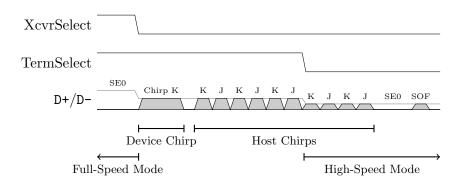

|    |       | A.1.4  | High Speed Detection Handshake                         | 71        |

|    | A.2   | USB (  | Communication Protocol                                 | 72        |

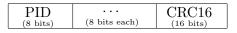

|    |       | A.2.1  | Packets                                                | 72        |

|    |       | A.2.2  | USB Frames and Microframes                             | 74        |

|    |       | A.2.3  | Transactions and Transfer Types                        | 74        |

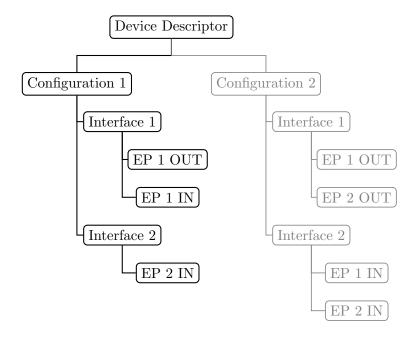

|    |       | A.2.4  | Device Descriptors                                     | 75        |

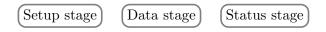

|    |       | A.2.5  | Control Transfers                                      | 77        |

|    |       |        |                                                        |           |

|    |       | A.2.6  | The usbmon Linux Kernel Module                         | 77        |

## CONTENTS

|            | A.2.8  | Bulk   | Transfer | s.    |        |       | •  | • • | • |  | • | • | • | • | <br>• | 82 |  |

|------------|--------|--------|----------|-------|--------|-------|----|-----|---|--|---|---|---|---|-------|----|--|

| A.3        | USB I  | Device | Classes  |       |        |       |    | • • | • |  |   |   | • |   | <br>• | 83 |  |

|            | A.3.1  | Com    | nunicati | ons E | Device | Class | 3. | • • | • |  |   |   | • |   |       | 83 |  |

| A.4        | Conclu | ision  |          |       |        |       | •  |     |   |  |   |   | • | • |       | 83 |  |

| Danksagung |        |        |          |       |        |       | 85 |     |   |  |   |   |   |   |       |    |  |

| Plagiat    | erklär | ung    |          |       |        |       |    |     |   |  |   |   |   |   |       | 87 |  |

# Deutsche Zusammenfassung

Ziel dieser Diplomarbeit ist der Entwurf und Test eines SpaceWire-Interface-Bausteins für die Simbol-X Satellitenmission. Simbol-X wird eine hohe spektrale und räumliche Auflösung im Energiebereich von 0.5–80 keV besitzen und damit eine wichtige spektrale Beobachtungslücke zwischen bisherigen Missionen wie XMM-Newton und Integral schließen. Dadurch wird es möglich sein Kenntnisse über Beschleunigungsmechanismen in den energiereichsten Systemen des Universums zu gewinnen, wie zum Beispiel der Entstehung von Jets aus Aktiven Galaktischen Kernen. Auch wird solch eine Mission zum besseren Verständnis von Mikroquasaren mit einem Schwarzen Loch oder Neutronenstern im Zentrum einer Akkretionsscheibe führen. Mit einiger Wahrscheinlichkeit wird es außerdem gelingen den Ursprung des Kosmischen Röntgenhintergrundes zu verstehen, da mit Simbol-X zum ersten Mal ein Instrument mit einer hohen Ortsauflösung im harten Röntgenbereich zur Verfügung stehen wird. Einige Quellen und Emissionsmechanismen sind in Kapitel 1 beschrieben, die Simbol-X Mission in Kapitel 2.

Simbol-X umfasst zwei Satelliten, einen mit einer Wolter Optik und einen mit dem Detektorsystem. Diese fliegen in Formation im Anstand von 20 m und fokussieren so die Röntgenstrahlen auf die Detektoren in der Fokalebene. Das Detektorsystem von Simbol-X besteht aus einem Hochenergiedetektor und einem Niederenergiedetektor. Die hier vorliegende Arbeit hat zum Ziel, den Niederenergiedetektor mit einer *Space Wire* Schnittstelle zu versehen um die Integration mit den übrigen elektronischen Komponenten des Satelliten zu ermöglichen. Der sehr modulare und leicht erweiterbare Entwurf ist nun als VHDL Code in einem FPGA realisiert und wird in Kapitel 3 genauer beschrieben.

Das SpaceWire Protokoll ist ein sich etablierender Kommunikationsstandard. Er wurde speziell entwickelt zur Benutzung in Satellitenmissionen und wird auch schon in zum Beispiel dem Herschel oder SWIFT Satelliten verwendet. Die hier dargelegte Arbeit beschreibt und testet das SpaceWire Protokoll, das hier in Tübingen zum ersten Mal Verwendung findet, im Zusammenhang mit der Entwicklung der Simbol-X Mission. Das SpaceWire Protokoll wird in Kapitel 4 erläutert. Um die hier entwickelte Schnittstellenkomponente von Simbol-X besser testen zu können, wurde ein spezieller SpaceWire-zu-USB Umwandler entwickelt. Der Universal Serial Bus (USB) wurde wegen seiner allgemeinen Verfügbarkeit und einfachen Handhabung gewählt, auch wenn die Details der Implementierung durch diese Wahl etwas komplexer wurden. Jedoch hat der SpaceWire-zu-USB Umwandler den zusätzlichen Vorteil eine generische Methode zu bieten, um große Datenmengen zwischen Software und Hardware auszutauschen. Der Konverter ist in Kapitel 5 beschrieben, und eine knappe aber detaillierte Zusammenfassung des USB Standards ist im Anhang A gegeben.

Leider wurde die Phase B von Simbol-X aus finanziellen Gründen abgesagt. Dennoch findet die hier vorgelegte Arbeit Verwendung insbesondere in Hinsicht auf das *International X-ray Observatory* (IXO), wo das *High Timing Resolution Spectrometer* (HTRS) das SpaceWire Protokoll verwenden und hier am Institut für Astronomie und Astrophysik Tübingen mit entwickelt werden soll.

# Preface

The letter I have written today is longer than usual because I lacked the time to make it shorter. — Blaise Pascal

The Simbol-X space mission is a planned space observatory for the 0.5-80 keV X-ray range. Simbol-X will consist of a satellite carrying the optics and another carrying two detectors, a low energy detector and a high energy detector. The two satellites will fly in formation to provide a long focal length of 20 m. Simbol-X would be the first mission to have a good angular resolution and sensitivity in the hard X-ray regime.

The intention is to look at some of the most energetic systems in the universe and further our understanding of the particle acceleration mechanisms active there. Jets are one of the most strange phenomena emanating from the hot center region of accretion discs around black holes and neutron stars in such systems as *Active Galactic Nuclei* and *Microquasars*. X-rays provide a unique view into that high-energy region with temperatures in excess of  $10^5$  K, where rotationally and gravitationally smeared out iron lines will be much better visible with an observatory such as Simbol-X. Also, the mission is needed to resolve the origin of the *cosmic X-ray background*, to better determine the parameters of recent *supernova remnants* in our galaxy, and to further understand the hot *intracluster gas* between galaxies. The emission mechanisms and sources are the topic of chapter 1.

The present work makes a small contribution towards reaching these goals by providing a *SpaceWire interface controller* for electronically connecting the low energy detector of Simbol-X to the rest of the spacecraft. The detector is a new silicon-based matrix with an extraordinarily high frame rate of 8000 frames per second that will allow a high time resolution in soft X-rays. To limit the data rates, it is essential to pre-process each frame and filter out only those pixel values that correspond to an actual photon event. The *interface controller* is designed to command that event pre-processing electronics (EPP) and to transfer the reduced science data via SpaceWire to the telemetry system of Simbol-X. The mission is described in chapter 2, the *interface controller* in chapter 3. Space Wire is an emerging standard analysed in this work. It is already used in recent space missions by ESA and NASA. In order to facilitate the development efforts for Simbol-X, a new SpaceWire-to-USB converter has been created that provides a general method for exchanging large amounts of data between hardware and software using the well-established Universal Serial Bus. The *SpaceWire* protocol is explained in chapter 4, the converter in chapter 5, and a concise introduction to the USB is given in appendix A.

Although it has been decided that there will be no phase B for Simbol-X, the present work continues to find its application in future missions such as the upcoming *International X-ray Observatory* (IXO).

#### 10

# Chapter 1

# X-ray Emission in the Universe

Simbol-X is a satellite space mission for imaging and spectroscopy in the soft to hard X-ray regime of 0.5–80 keV. In this chapter some of the emission mechanisms and sources that Simbol-X could help understand are summarized.

# 1.1 Emission Mechanisms

#### 1.1.1 Blackbody Radiation

A body in thermal equilibrium radiates an electromagnetic spectrum dependent on its temperature. Ignoring surface effects specific to the material, all stationary bodies radiate the same spectrum given by Planck's Law[1]

$$B_{\nu} = \frac{2h\nu^3}{c^2} \frac{1}{e^{h\nu/kT} - 1},$$

or rewritten in terms of the photon energy  $E = h\nu$

$$B_E = \frac{2E^3}{h^3c^2} \frac{1}{e^{E/kT} - 1}.$$

Dependent on the temperature, the maximum of the spectrum is at the photon energy

$$E_{max} = 2.821 \, kT$$

$$= 2.431 \cdot 10^{-7} \, \mathrm{keV}\left(\frac{T}{\mathrm{K}}\right),$$

with the Boltzmann constant  $k = 1.3806 \cdot 10^{-23} \text{ J/K}$ . Temperatures around  $10^5 \text{ K}$  peak around 0.024 keV, contributing with an exponential tail to soft X-rays.

#### 1.1.2 Inverse Compton Scattering

In 1923 A. H. Compton observed the scattering of a photon off an electron, now called the *Compton Effect*. Removing the final 4-momentum of the electron, 4-momentum conservation yields the relativistic equation

$$p^{\mu} \cdot p'_{\mu} = q^{\nu} \cdot (p_{\nu} - p'_{\nu}),$$

where p and q are the 4-momentum of the photon and electron before the collision, p' that of the photon after the collision. This equation is valid when  $\gamma \hbar \omega \ll m_e c^2$ , that is, the energy of the photon as seen from the electron is much less than the rest energy of the electron.

The process is called Compton scattering, when the photon looses energy to the electron, e.g. when the electron is initially at rest and then moving. *Inverse* Compton scattering is when the electron population is at a much higher energy than the photons. In that case, low energy photons are upscattered to higher energies

$$E' \simeq \gamma^2 E,$$

where  $\gamma$  is the time component of the 4-velocity better known as the gammafactor of the electron, and E and E' are the energies of the photon before and after the collision. For a highly relativistic population of electrons this can up-scatter photons to keV and even TeV energies.

#### 1.1.3 Synchrotron Radiation

Synchrotron radiation is produced when charged particles such as electrons are accelerated in a magnetic field, following the field lines in a helix-like pattern due to the Lorentz force

$$\frac{dp^{\mu}}{ds} = qF^{\mu\nu}v_{\nu},$$

where ds is the spacetime interval along the path, q is the charge, F is the electromagnetic field, and v the 4-velocity. In radio a highly polarized beam can be observed. At high energies the spectrum is a power law[13]

$$B \propto E^{-\alpha},$$

where  $\alpha$  is in the range 0.5 - 1.

#### 1.1.4 Bremsstrahlung

Charged particles emit electromagnetic radiation when accelerated. The power emitted by a single charge is given by Larmor's equation

$$\frac{dE}{dt} = \frac{2\,q^2\dot{v}^2}{3\,c^3}.$$

This occurs for instance in a hot plasma where electrons are accelerated in the field of the ions. The resulting spectrum features an exponential cut-off towards higher energies.

#### 1.1.5 Emission and Absorption Lines

Discrete emission and absorption lines can be observed in the spectrum for atomic transitions. For X-ray astronomy the  $K_{\alpha}$  and  $K_{\beta}$  fluorescent lines of iron with energies of 5.9 keV and 6.49 keV are of particular interest, where an electron transitions into the K shell from the L or M shells.

The nuclear decay of  $^{44}$ Ti into  $^{44}$ Ca also produces discrete emission lines particularly at 68 keV and 78 keV, which is important for understanding the origin of calcium in supernova remnants.

# 1.2 Astronomical Sources of X-rays

This section provides an overview over some of the more common X-ray emitting objects.

### 1.2.1 Active Galactic Nuclei

Many if not all galaxies feature a central black hole with masses of  $10^6$ – $10^9 \,\mathrm{M}_{\odot}$ . Whereas the black hole in the center of the milky way is relatively quiet, *Active Galactic Nuclei* (AGN) accrete  $1-3 \,\mathrm{M}_{\odot}$  every year, producing accretion discs and massive outflows in the form of jets that can span thousands of parsecs.

AGN frequently radiate at or above the Eddington luminosity given by the maximum that a spherically symmetric accreting object of mass M can radiate:

$$L_{\rm Edd} = \frac{4\pi c \, G \, M \, m_p}{\sigma_T},$$

where  $m_p$  is the mass of a proton and  $\sigma_T$  is the Thomson cross section for the collision between a photon and an electron. It is given when the

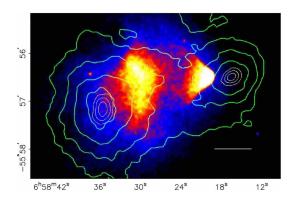

Figure 1.1: This is a composite image of Centaurus A at a distance of 3.4 million parsec. In blue is the X-ray image from Chandra, in orange the submillimeter taken with the Atacama Pathfinder Experiment, and in white and brown the optical view from the Max-Planck telescope. (Credit: X-ray: NASA/CXC/CfA/R.Kraft et al.; Submillimeter: MPIfR/ESO/APEX/A.Weiss et al.; Optical: ESO/WFI)[6].

gravitational force and the radiation pressure on the infalling material are equal. In AGN, the material is not spherically falling onto the central black hole, but due to angular momentum and friction it is forming a hot accretion disc with temperatures exceeding  $10^5$  K.

AGN are classified into three basic types Seyfert 1, Seyfert 2, and Blazars. These are distinguished by the visibility of the nucleus and our viewing angle. The nucleus of Seyfert 1 galaxies is mostly absorbed by a gaseous ring. In Seyfert 2 galaxies the view to the nucleus is unobstructed, whereas with blazars we are looking directly into the jet. AGN show a time variability of their luminosity on the order of hours, resulting in an estimated size of a few astronomical units.

Shown in Figure 1.1 is an X-ray–submillimeter–optical composite of the Seyfert 1 type galaxy Centaurus A. Much of the optical range is absorbed by a ring of gas. The submillimeter radio observation is mostly associated with the outer lobes at the end of the jets, and the X-ray observations show the jet where it is still highly relativistic and the energetic inner regions of where it is produced.

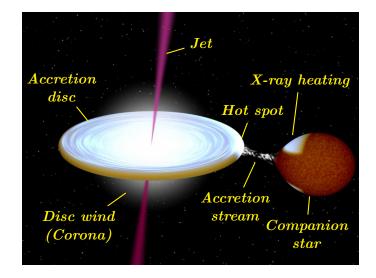

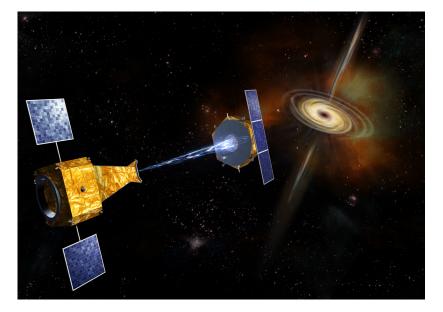

Figure 1.2: An artists impression of the microquasar GRS1915+105. Matter is accreted by the compact black hole via Roche-Lobe overflow from the companion star forming a hot spot where the matter hits the accretion disc. [3]

### 1.2.2 Cosmic X-ray Background

The cosmic X-ray background (CXB) peaks around 30 keV. Its origin is still unclear. One possible source could be a population of AGN with a hard spectrum that are too faint to detect in soft X-rays with Chandra or XMM-Newton. Simbol-X could be able to resolve those and contribute to the understanding of the CXB.

## 1.2.3 X-ray Binaries

In X-ray binaries a neutron star or black hole orbits a companion with an orbital period of typically a few days. When the companion star is so large that its surface is close to the Lagrange point  $L_1$ , matter may flow from the star to the compact object via Roche-Lobe overflow, as pictorially displayed in Figure 1.2 for GRS 1915+105. Thermal X-ray emission is produced by the accretion disc close to the black hole reaching temperatures up to  $10^5$  K. The jet is primarily associated with radio waves, but closer to the black hole the electrons are relativistic enough to produce synchrotron radiation in the X-ray band, while farther out the emission reduces to infrared and radio. X-ray emission is also produced via inverse Compton up-scattering of low energy photons in the hot corona and directly in the jet. Should the compact object be a neutron star, X-rays may also be produced when the

matter falls in an accretion column onto the surface of the star.

Emission lines from highly ionized iron have been observed. Their energy profile suggests that they are originating close to the compact object, since they are Doppler shifted, beamed, and anti-beamed by the rotation in the accretion disc, and red shifted by the gravitational field. However, the resolution of the spectra taken with current missions is not very satisfying. With the higher sensitivity of Simbol-X, much better spectra could be obtained.

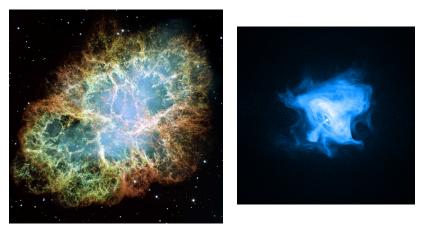

### 1.2.4 Supernova Remnants

Supernova remnants are another source of X-rays where the Simbol-X mission could contribute to their understanding. In the constellation of Taurus a supernova exploded that was observed in 1054 A.D. and left behind the Crab nebula with a fast rotating neutron star, the pulsar, in the center, see Figure 1.3. The material outflow is directed by strong magnetic fields towards the poles and the equatorial plane of the pulsar. The X-ray radiation is produced by a shock where the ejected material from the pulsar interacts with the surrounding gas, and by the beamed synchrotron radiation of electrons following the magnetic field lines.

### 1.2.5 Intracluster Gas

A galaxy cluster typically consists of only about 1% matter visible in the optical range. Another 5–15% is hot intracluster gas with temperatures of  $10^7$ – $10^8$  K that can be seen in X-rays, see Figure 1.4. The rest of the mass is called *dark matter* the nature of which is still unknown.

(a) HST mosaic

Figure 1.3: The Crab nebula (a) in an optical mosaic by the Hubble Space Telescope and (b) in soft X-rays by Chandra. The images are approximately at the same scale and orientation. (Images courtesy of NASA/STScI[11] and NASA/CXC/SAO[10]).

Figure 1.4: The image shows the merging galaxy cluster 1E0657-558 as observed by Chandra. The more massive eastern cluster has a temperature of 14 keV while the less massive about 6 keV. The contours show the mass distribution of the clusters as determined by weak gravitational lensing.[2]

# Chapter 2

# The Simbol-X Mission

In this chapter a brief introduction to the Simbol-X mission in context of other astronomical instruments of the past is given.

# 2.1 The Rise of Astronomical Instruments

With the invention of the telescope by Lipperhey at the beginning of the 17<sup>th</sup> century, the examination of the celestial sphere could be carried out in unprecedented detail giving rise to the discovery of the moons of Jupiter when Galileo Galilei first pointed his telescope at the sky. Subsequent refinements in telescope technology further contributed to the establishment of the Copernican world view that overthrew that of the late ancient Greeks. With the invention of the Newtonian reflector, much larger apertures became possible like Herschel's telescope that was finished in 1789, and the 5 m Palomar Observatory finished in 1948.

It is only in the 20<sup>th</sup> century that astronomical observations in other wavelengths could be performed. It started in 1931 when Karl Jansky of Bell Labs discovered the center of the milky way in radio waves.[15]

However, since much of the electromagnetic spectrum is blocked by the atmosphere, longer observations in the infrared, ultraviolet, X-ray, and gamma-ray bands only became possible with the advent of space flight, although modern ground based Cherenkov telescopes use the earths atmosphere as a detector medium for ultra high energy gamma-rays.

## 2.2 Previous X-Ray Missions

First X-ray observatories were carried with balloons and rockets in the 1960s. The following missions mark the development of space-borne X-ray observatories from its beginning in the second third of the 20<sup>th</sup> century up to the present.

- The first satellite dedicated to X-ray astronomy is *UHURU* launched in 1970 from Kenya. It was sensitive to about 0.5 mCrab in the 2–20 keV range at an angular resolution of about 30'.

- *Einstein* was the first fully imaging X-ray satellite launched in 1978. It had an angular resolution down to 2" in the soft X-ray range 0.15–3 keV.

- The *Roentgen Satellite* (ROSAT) from 1990–1999 conducted an all-sky survey in the soft X-ray regime.

- The Rossi X-ray Timing Explorer (RXTE) launched in 1995 provided astronomers with a high time resolution of up to 1 µs at 2–250 keV.

- With the launch of BeppoSAX in 1996, a satellite with an angular resolution of 9.7', imaging capabilities were available up to 10 keV.

Only RXTE and the following more recent missions are still in operation today:

- The Chandra X-ray Observatory is characterized by a high angular resolution of almost 0.5'' in the 0.1-10 keV range. It was launched in 1999.

- Launched in the same year as Chandra, the X-ray Multi-Mirror Mission (XMM-Newton) has a lower angular resolution of 6", but a much higher sensitivity. Its energy range is slightly larger from 0.1–15 keV.

- Onboard the International Gamma-Ray Astrophysics Laboratory (IN-TEGRAL) is the Joint European X-ray Monitor sensitive up to 35 keV at an angular resolution of 3'. Also onboard is an instrument with 12' resolution starting at 15 keV. It was launched in 2002.

- Finally, *Suzaku* contains a spectrometer for soft X-rays with a spatial resolution of 1.8', and a non-imaging detector for hard X-rays.

With Chandra and XMM-Newton two similar missions with a high angular resolution in soft X-rays below 10 keV are available that have contributed greatly to our understanding of soft X-ray sources up to about 15 keV. These

Figure 2.1: An artists expression of the Simbol-X mission. (Credit: CNES / Oliver Sattler)

missions provide accurate data in the soft X-ray regime. Missing from this list is a detector system with a high angular resolution better than 20" and a high sensitivity in the hard X-ray band. Simbol-X intends to fill that gap.

# 2.3 Simbol-X

Simbol-X is an astronomical space mission in the low to hard X-ray regime. Started as a French-Italian cooperation, Simbol-X is a two-spacecraft mission, where one satellite carries a focusing Wolter optics and the other the X-ray detector positioned in the focal plane. A graphic is shown in Figure 2.1. Its launch was planned for 2014.

It is unique in that it would be the first instrument with a good spatial resolution and sensitivity in the hard X-ray range above 10 keV.

In the following, a very short introduction to the satellite's optics, detector system and electronics is given.

## 2.3.1 Wolter Optics

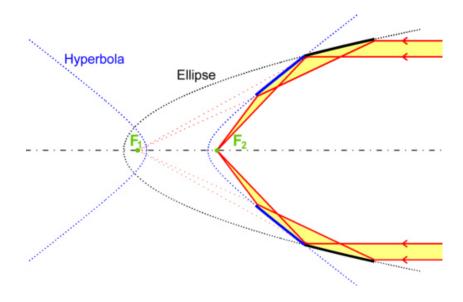

X-rays cannot be focused with ordinary lenses or mirrors. However, total internal reflection occurs at angles of the order of  $1^{\circ}$ , less for harder radiation. A Wolter optics is a mirror arrangement named after its inventor Hans

Figure 2.2: Wolter type I optics. (Image from [12])

Wolter (1911–1978) that can be used to focus X-rays using total internal reflection.

In principal, a Wolter type I optics consists of 2 mirrors, an ellipse and a hyperbolic as shown in Figure 2.2. A type I Wolter optics can be stacked many times as concentric shells that together yield a larger total aperture. Due to the nature of total internal reflection of X-rays, a Wolter optics system has the following properties that determine its geometry.

- The small reflection angle results in a large focal length, especially for hard X-rays. To achieve that, the Simbol-X optics are on a separate spacecraft flying in formation with the detector unit at a distance of 20 m as shown in Figure 2.1.

- The variance of the maximum total internal reflection angle with the photon energy results in a smaller effective aperture for harder X-rays as the outer shells no longer focus.

To achieve the scientific mission, Simbol-X was designed with 100 concentric shells, the largest  $65 \,\mathrm{cm}$  and the smallest  $26 \,\mathrm{cm}$  in diameter, with a focal length of  $20 \,\mathrm{m}$ .

### 2.3.2 X-ray Detector System

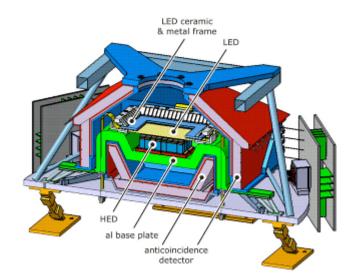

The detector system in the focal plane consists of two  $128 \times 128$  X-ray detectors. The low energy detector (LED) becomes transparent for higher

energy photons, so it can be positioned in front of the high energy detector (HED) as shown in Figure 2.3. The two detectors are surrounded by an anticoincidence detector (ACD) for filtering particle background events and thus significantly reducing the background. The Simbol-X low energy detector is in so far unique in that it would be the first with an active anticoincidence shield. In addition, it was discussed to use a proton deflector to reduce the background from low energy protons funneled onto the detector by the optics. This would also reduce the degradation of the detector by such protons.

The detectors have the following characteristics.

- The LED is sensitive in the range 0.5 keV–20 keV. A pixel of the matrix consists of concentric drift rings collecting the electrons at the center where a DEPFET (*Depleted P-channel Field Effect Transistor*) is used to detect the amount of electrons freed by the incoming photon. Each pixel has a size of 625  $\mu$ m × 625  $\mu$ m. It is read out at a rate of 8000 frames per second.

- The HED has a range up to 80 keV in hard X-rays. The detector material is made up of CdTe.

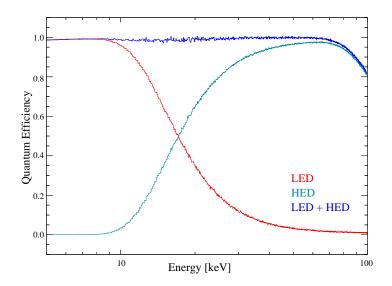

- Together, the two detectors give a nearly 100% quantum efficiency across the X-ray range up to 80 keV as shown in Figure 2.4.

- The ACD catches particles from everywhere except where the photons from the optics are coming in. Comparing the time of an event in the ACD with the time of pixels from the LED and HED allows to classify these as background events and be discarded for most science measurements.

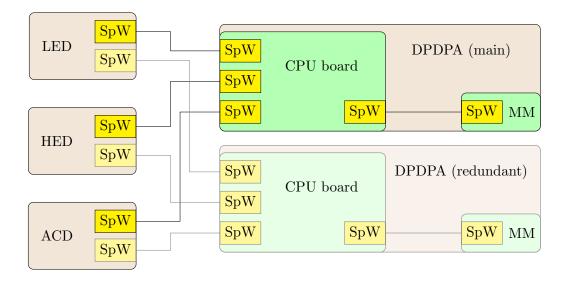

The LED, HED, and ACD are connected via a SpaceWire link to the central DPDPA processing board as shown in Figure 2.5. The software running on the DPDPA CPU board has access to a several hundred megabyte large mass memory. It will compute offset and threshold maps, command each detector to start and stop sending science data, and correlate events from the anticoincidence detector with the pixel events from the detectors. From the DPDPA board science and housekeeping data are transferred to the spacecraft telemetry system and from there to ground.

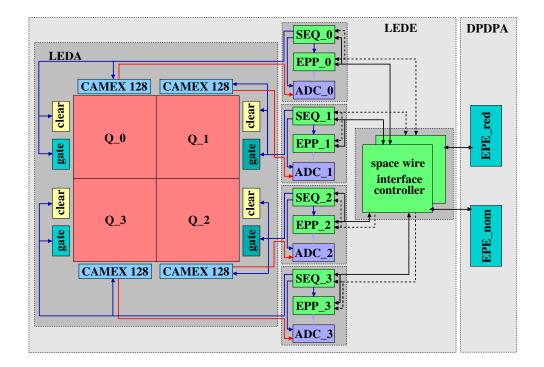

The LED electronics (LEDE) are shown in Figure 2.6. It is the purpose of the interface controller developed in this work to provide the LED with a SpaceWire interface to the DPDPA board, and to convert the science data into a standardized format.

Figure 2.3: The Simbol-X detector geometry. X-rays coming in from the top hit the low energy detector (LED) first. Higher energetic X-rays continue through to the high energy detector (HED). For detecting particles from the sides or bottom, the entire detector system is surrounded by an anticoincidence detector. An aluminium base plate transports heat to the outside to keep the detector temperature below  $-40^{\circ}$ C. (Credit: CEA / Jerome Martignac)

Figure 2.4: The combined quantum efficiency of the LED and HED add up to almost 100% as shown in this simulation by C. Tenzer.

Figure 2.5: Simbol-X detector connections. The CPU board is connected via SpaceWire links to each of the three detectors, and has access to a mass memory unit (MM), which is also part of the DPDPA. Every detector has a redundant SpaceWire interface controller that connects to the redundant DPDPA shown subdued in the figure. Not shown is the connection with the telemetry electronics. (adapted from Simbol-X Detector Payload SpaceWire Utilisation Requirements [4] Figure 1-1)

Figure 2.6: LED electronics overview. The  $128 \times 128$  detector matrix is split in 4 quadrants  $Q_0$ ,  $Q_1$ ,  $Q_2$ , and  $Q_3$ . Each quadrant is controlled by two switchers, gate and clear. The gate switcher enables an entire row of a quadrant, so that the energy deposited in each pixel can be read out by the CAMEX (Charge Amplifying Multiplexer). The clear switch flushes the electrons in a row of DEPFETs for the next frame. The analog pixel values from the CAMEX are transferred to an ADC for each quadrant, where the event preprocessor (EPP) filters for the pixels corresponding to a photon event. The switchers, CAMEX, ADC, and EPP receive their timings from the sequencer (SEQ) of each quadrant. The interface controller transfers the data from each quadrant to the DPDPA, and accepts commands to power up and configure the low energy detector electronics. Should the nominal interface controller fail, the DPDPA can enable a redundant one. (Graphic courtesy of Thomas Schanz)

# Chapter 3

# The Interface Controller

The purpose of the interface controller is to provide a simple and standardized interface to the low energy detector electronics of Simbol-X. The design is realized in an FPGA with input and output ports for each of the components of the detector readout electronics. In this chapter the requirements on the interface controller are described, then the overall design principles, and finally the specifics of each component.

## 3.1 Interface Controller Requirements

The interface controller (IFC) provides the low energy detector of Simbol-X with a SpaceWire interface to the rest of the spacecraft, the DPDPA. As such, it needs input and output ports for every component of the low energy detector, plus those needed for the SpaceWire communication with the rest of the spacecraft.

Figure 3.1 gives an overview of the components the interface controller needs to communicate with. The following input/output port considerations need to be made for every quadrant.

• The sequencer and the EPP are combined onto the same board, so that a single SPI link is sufficient for control commands towards the detector. The SPI link is used to configure and command the sequencer and the EPP. Most importantly it is this link via which the IFC must upload offset and threshold maps for the EPP, and it needs to command the sequencer when it should start and stop operating the detector readout electronics. The SPI link needs 3 output and 1 input signal.

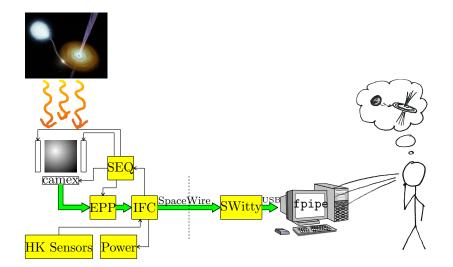

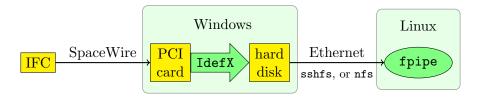

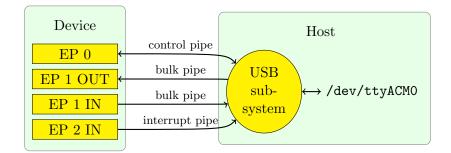

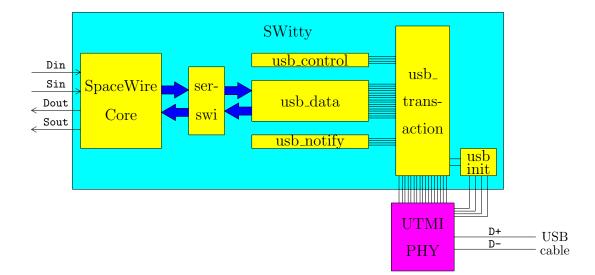

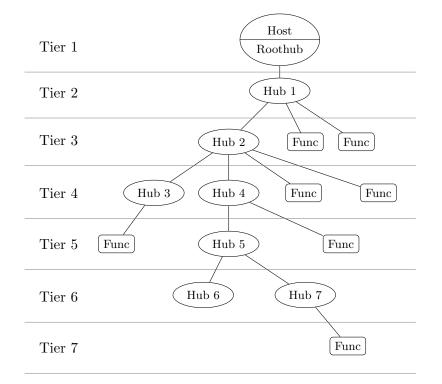

Figure 3.1: LED electronics overview. Starting at the top left, X-rays from a binary system hit the detector matrix which is above the CAMEX that amplifies the raw pixel values. To each side of the detector matrix are switchers to control the detector read out. The amplified pixel values from the CAMEX are digitalized with an ADC (not shown), and sent to the event-preprocessor (EPP). The switchers, CAMEX, and EPP are controlled by the sequencer (SEQ). The interface controller (IFC) collects the science data from the EPP, sends commands to the sequencer, controls the power, and collects housekeeping (HK) sensors data. The communication with the rest of the spacecraft is done via a SpaceWire link. Shown here is a setup as is planned in the laboratory for testing, where the SpaceWire communication is transferred by SWitty, explained in chapter 5, to a computer via the USB, and analysed with the fpipe analysis software.

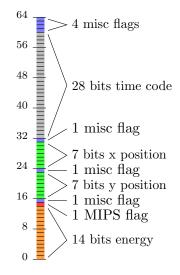

- The EPP reduces the detector output to only those pixels that correspond to a photon event. Each pixel is encoded in a 64-bit format that includes a time code, the position, the energy, and the type of the pixel. In order not to use up too many I/O ports of the interface controllers' FPGA, a 16-bit parallel bus is envisioned for the data transfer of the pixels from the EPP, controlled by 2 extra signals.

- The housekeeping and power sensors were not set as of this writing, but to save FPGA I/O ports, an analog multiplexer is added to the interface controller board. It directs analog sensor signals onto a single ADC that, too, will be on the IFC board.

- The interface controller must also set the power for the detector. However, the power supply interface was too early in its development to be considered for the IFC at the time of this writing.

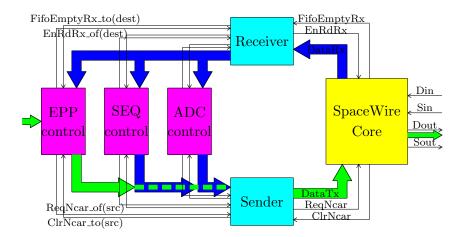

Figure 3.2: IFC internal overview. On the right, the SpaceWire core with the SpaceWire signals is shown. The Sender and Receiver components distribute and collect packets to and from the \*\_control components that do the actual work of communicating with the components of the low energy detector. Not shown are the external signals for that communication. The thick arrows in light color depict the path of science data from the EPP through the interface controller.

• Finally, the interface controller will be used to carry a clock signal to the EPP. However, this clock signal will not affect the IFC directly. Instead, it is distributed through signals electrically separate from the IFC.

# 3.2 General IFC Design Considerations

At its core, the interface controller must act as a router to the various components of the low energy detector. The basic design is shown in Figure 3.2. Control components provide the low-level interaction with each LED component. The receiver component is responsible for distributing packets from the SpaceWire core to the individual control components. Similarly, the sender is responsible for collecting the packets from the control components and sending them to the SpaceWire core.

The interface controller has undergone a complete rewrite since a first working version was in place. Compared to that, the current design has the following advantages.

• Debugging and testing of IFC components is extraordinarily easy.

- There are no complicated interrelationships between components and internal signals.

- The IFC is easily extensible.

These three advantages have resulted in a nearly bug-free implementation. They are the result of some general design principles, some of them created as a response to the first version of the interface controller, some of them well known in the software programming community. Even though that first version of the interface controller exhibited a highly modular design, it is only with the help of these guiding principles that a truly workable design could be created. Those principles shall be described in the next few sections.

## 3.2.1 Equality

All components are created equal. What this means is that the components are in no particular hierarchical order in and of themselves. It is only their function that determines their place inside the interface controller.

The principle of equality entails that the communication between the individual components must be standardized. Ignoring external signals, the entity of each component has been chosen to match precisely the host-side interface of the SpaceWire core. It consists of a 9-bit data bus and two signals, FifoEmptyRx and EnRdRx, for receiving packets, and a 9-bit data bus and the signals ReqNcar and ClrNcar for sending packets.

The practical implication is that each component can be connected directly to the SpaceWire core and be tested separately from all other components.

### 3.2.2 Uniqueness

The principle of uniqueness says that code should not be duplicated. The principle can be further interpreted to mean that the *idea* expressed within a piece of code should occur only once. Duplication early in the development means that changes in one copy might not be applied to another copy, and the relationship between the two copies becomes unclear as the code evolves. This is hampering development especially when ideas are changing, since every piece of code needs to be reviewed for subtle changes.

Uniqueness of code has played a central role from the very beginning of the development of the interface controller. Early versions, however, broke the principle with regards to the uniqueness of ideas expressed in the code. It is uniqueness of code *and* of ideas that leads to a clean modularization

30

framework. The principle demands that similar but distinct functions be merged together or split up further. Uniqueness is the driving force behind factorization of a design into independent modules with clean interfaces.<sup>1</sup>

For hardware, the situation is much reversed. Using the same components in many parts of the design means that optimization can be directed towards fewer distinct elements. Should the element be designed in a hardware description language, this leads us back to the principle of uniqueness, where concentrating on a single implementation of a component instantiated many times greatly eases development.

## 3.2.3 Simplicity

Simplicity is a well known term in software development. It can mean many things including minimalism, symmetry, and elegance. It also ties in very closely with the ideas of uniqueness and modularity, as both these demand that complications are coded only once, leading to a simpler overall design.

When uniqueness is impossible, such as using the same interface between all the components, then simplicity demands that this interface be a simple interface. In the case of the interface controller, it entailed forbidding complicated interrelationships between the various components, and symmetrizing the relationship between receiving and transmitting data busses.

Simplicity cannot be pinpointed easily. It pervades the design on every level. When complications are hidden away in submodules, simplicity demands an interface for these submodules that can be easily described and shared among developers. What this usually means is that each module should do only one thing, and do that well.<sup>2</sup>

## 3.2.4 Beauty

The combination of the principal ideas of equality, uniqueness, and simplicity has resulted in a highly modular design. The three principles are in many ways building on top of the usual mantra of a modular design with independent components, but in some ways they are more general. Indeed, it could well be argued that these might set the very foundation of which modularity is perhaps the best solution.

Perhaps the most important consequence is that the code in its entirety may be called beautiful. Beautiful code is simple code. Beauty is achieved when simple code snippets are combined to create a design capable of much

<sup>&</sup>lt;sup>1</sup>Hence, this subsection may also be called "Modularity is not enough".

<sup>&</sup>lt;sup>2</sup>This is one of the basic philosophies behind UNIX.

Table 3.1: Transmitter and receiver host data interface coding. The MSB, e.g. DataRx(8), is leftmost, the LSB rightmost. (Table 7, page 54 in ECSS)

| DataRx/DataTx | Meaning    |

|---------------|------------|

| 0xxxxxxx      | 8-bit data |

| 1xxxxxx0      | EOP        |

| 1xxxxxxx1     | EEP        |

more than its individual components. That is, beauty ensues when removed complexity results in greater applicability. It is the beauty of small but generally applicable code that drives development. The practical result is that it is a delight to maintain and extend the design.<sup>3</sup>

## **3.3** IFC components

The interface controller consists of the SpaceWire core component, the Receiver and the Sender, and multiple control components. In this section these components of the interface controller will be described in more detail.

### 3.3.1 SpaceWire core

The SpaceWire core component used was developed by Frédéric Pinsard and Christophe Cara at CEA. The host-side interface exported by this component is used throughout the design of the interface controller.

There are, actually, two interfaces. One for the receiving line, another for the transmitting line, denoted by appending Rx and Tx to the respective signal names. The data is published via the signals DataRx and DataTx. These are 9-bit data busses, and as shown in table 3.1, the 9<sup>th</sup> bit, e.g. DataRx(8), is used to distinguish between a data character and a control character. If that bit is high, then it is a control character, and the LSB distinguishes between a normal end-of-packet and an error-end-of-packet. If the MSB is low, the remaining 8 bits constitute a data byte.

The interface controller is notified of a new character by the SpaceWire components two control signals FifoEmptyRx and EnRdRx. They are used just like the interface to a FIFO that is filled with SpaceWire characters coming over the SpaceWire link, and emptied by the interface controller. On the transmitting side, there are the two signals ReqNcar and ClrNcar with the same idea but slightly different semantics as the signals on the

$<sup>^{3}\</sup>mathrm{It}$  is somewhat unfortunate that be autiful code is code that does not need much maintenance.

Figure 3.3: The Receiver distributes packets to their respective control component.

receiving side. To merge the two, the signal FifoEmptyRx should have been negated, i.e. FifoNotEmptyRx.

The SpaceWire component is the first to receive commands over the Space-Wire link. As such, it is viewed as the master to the other components of the interface controller.

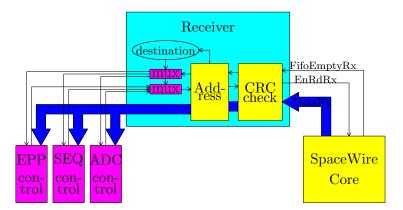

### 3.3.2 Receiver

The purpose of the receiver component is to distribute incoming packets to their respective control component. In doing that, the receiver is also stripping the header and footer from each packet.

Although the packet formats were not finalized as of this writing, the header will have the same structure for all packets. It will contain a byte identifying the LED as its destination. For compatibility with specifications, another byte will specify that the packet is in a custom format. A third byte is used for the packet type distinguishing packets for housekeeping and science packets. It might also be used as a logical address for identifying the control component responsible for the packet.

The footer consists of a single CRC8 byte for checking the integrity of the packet. It is the responsibility of the receiver to check that the CRC is correct and to provide the control components only with the cargo of the packets. It does this by controlling a multiplexer via the register destination that transfers the FifoEmptyRx and EnRdRx signals to the specified control component. This is shown in Figure 3.3. In this way, the control components can essentially "see through" the receiver as if directly connected to the

Figure 3.4: The Sender essentially multiplexes the access to the SpaceWire core.

SpaceWire core.

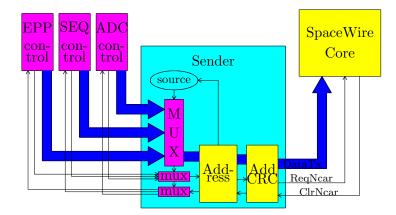

## 3.3.3 Sender

The sender component does the opposite of the receiver. It polls which control component has a packet to send and grants it access to the SpaceWire core, adding an appropriate header and a CRC8 footer to each packet. The internal setup of the sender is very similar to that of the receiver, and it is shown in Figure 3.4.

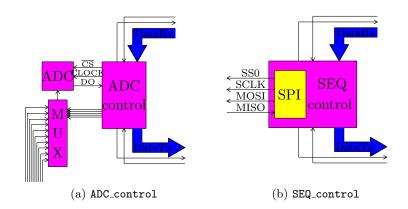

## 3.3.4 ADC\_control

ADC\_control is the prototype for the housekeeping control component. Housekeeping data includes values from temperature, voltage, and current sensors, the most prominent probably being the one reporting the temperature of the detector matrix. Which values exactly will be needed was not clear yet as of this writing and will be determined during detector operation in the laboratory.

To save ADCs and FPGA I/O ports, most analog sensor values will be multiplexed onto a single ADC. The design is shown in Figure 3.5a. The ADC\_control component sets an address on the multiplexer, which then puts the signal from the selected sensor on the ADC input. The control component then proceeds to read out the digitalized value from the ADC via the signals shown in the figure.

Figure 3.5: (a) Analog sensor signals from the bottom left are multiplexed onto an ADC. The component ADC\_control inside the FPGA sets an address on the multiplexer, and reads out the converted value via a standard ADC interface. (b) The sequencer control component allows the DPDPA software on the other side of the SpaceWire link to send commands directly to the sequencer, providing an SPI converter as it does so.

### 3.3.5 SEQ\_control

This control component interacts with the sequencer. Packets coming over the SpaceWire are sent to the sequencer via an SPI bus. The interface controller acts as a kind of tunnel to the SPI interface of the sequencer, so the DPDPA software can essentially communicate directly with the sequencer.

The basic setup is shown in Figure 3.5b. Whether a more complicated setup is necessary or even desired is yet to be determined. The current setup might have the drawback of taking a long time to upload an offset or threshold map as each pixel needs to be set individually. Every command is 6 bytes long. Adding to that 3 bytes for the header, 1 for the CRC sum, and roughly half of one for the end-of-packet, adds up to 10.5 bytes per pixel. For a total of 4096 pixels, that makes at least 43008 bytes per map. At a rate of  $2 \,\mathrm{MB/s}$ that takes 22 ms over the SpaceWire. The SPI link is slower, and takes  $6 \times 8 = 48$  SPI clock cycles per command. For successful operation, the SPI clock is lowered to  $3.75 \,\mathrm{MHz}$ , making  $12.8 \,\mu\mathrm{s}$  per command, or about 53 ms per map. Sending the 2-byte status result received while transmitting over the SPI back over the SpaceWire takes another 13.3 ms per map. In total, uploading an offset or threshold map should take about 88.3 ms. Even though there will be some extra latencies introduced that are not included in this calculation, there does not seem to be any pressing need for a more complicated setup.

Figure 3.6: The figure shows the preliminary assignment of each of the 64 bits for every pixel. Small ticks mark bit boundaries, large ticks mark byte boundaries.

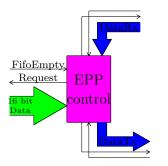

### 3.3.6 EPP\_control

The EPP\_control component collects the science data from the event preprocessor, packages them in a standardized format, and sends them off over the SpaceWire to the DPDPA software. The control of the EPP is done via the sequencer, and is not part of this component.

The standardized format is made up of 64 bits for every pixel. The information encoded in these 64 bits is shown in Figure 3.6 as was agreed upon at the time of this writing. The data from the EPP is very similar, and contains for each valid pixel a time code, the energy, the position, and various miscellaneous flags subject to change. The standard format has been deliberately chosen with the following points in mind.

- The time code, x, y positions, and energy are byte aligned, because that makes for much easier processing in software.

- The MIPS flag has been chosen as an extra bit for the energy, so that a simple check of the energy is all that is necessary for the DPDPA software to distinguish good events from MIPS.

- The quadrant number is within the 7<sup>th</sup> bits of the x and y positions, making the position a natural number across the entire  $128 \times 128$  detector matrix.

Figure 3.7: The EPP\_control component collects the science data from the event preprocessor over a 16 bit data bus with an interface reminiscent of a FIFO.

• To allow for additional miscellaneous flags, only the first 28 bits of the EPP time counter are transmitted with every pixel. This would have a wrap-around time of 13.42 s. The rest of the time code can then be retrieved via other means.

The 64 bits per pixel are envisioned to be transmitted over a 16 bit bus as shown in Figure 3.7, where each signal is LVDS encoded for better electromagnetic compatibility.

In order to test the EPP\_control component a simulator was written. The simulator will be more closely described in section 3.4.1. Even though the data format from the simulator is somewhat different, it could be shown that the interface controller can sustain data rates well above the maximum 2 MB/s of the SpaceWire link.

## 3.3.7 PWR\_control

This component controls the power to the LED. It does not exist yet, as it only makes sense to develop when more details about the power interface are available. It is mentioned here as it is an important part of the interface controller should Simbol-X fly.

# 3.4 Additional components for testing

In this section two control components, ECH\_control and SIN\_control, and a simple EPP data simulator used for testing purposes are introduced.

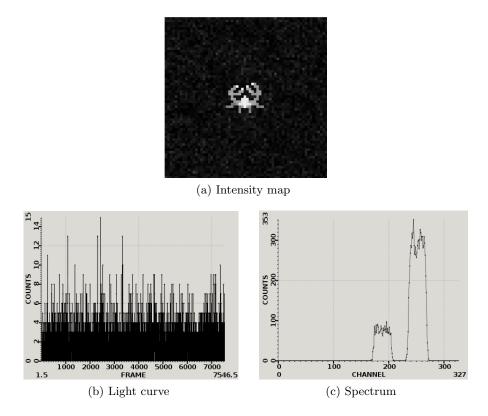

Figure 3.8: The Crab lifts its right claws.

### 3.4.1 EPP data simulator

At the time of this writing, the hardware to connect the EPP with the interface controller was not available. As a consequence a simple simulator for the data was written as a subcomponent of the EPP\_control module. The raw pixel energy values are created from three sources listed below. In the following, data is a VHDL variable holding the raw pixel value, and rand is a pseudo-random number generated from a 63 bit linear feedback shift register (LFSR). It has a 5 bit range, that is from 0 to 31.

• Offset: data <= 0x133 + rand;

The offset is valid for every pixel. It corresponds to the current measured in the detector when there was no photon event.

• Image: data <= 0x1F0 + rand;

To make things more interesting, a PNG file containing a picture of a well known X-ray source is loaded at VHDL synthesis time. The RGB value of each pixel in the image determines the intensity. The resulting image is shown in Figure 3.8a.

### 3.5. SUMMARY

• Background: data <= 0x22F + rand;

The background is also valid for all pixels, but it is not set every single frame. Instead there is a randomization resulting in about 2 to 3 pixels per frame contributing to the background.

An intensity map, a light curve, and a spectrum in arbitrary units are shown in Figure 3.8 as screen shots from the **fpipe** analysis software.

The EPP data simulator acts as a source of data. The rate of data transmission can be throttled if desired or needed. The simulator has made development somewhat of a delight, and the slightly asymmetric nature of the image proves that the entire chain from the interface controller to the analysis software is interpreting the X and Y coordinates of the pixels correctly.

# 3.4.2 ECH\_control

The ECH\_control component echoes everything it receives back over the SpaceWire. It is very handy for testing the SpaceWire connection in all rigor. Its main use is for testing when the SpaceWire core is replaced by SWitty, which is a SpaceWire-to-USB converter described in chapter 5.

### 3.4.3 SIN\_control

The SIN\_control component acts as a sink accepting all data, sending none. It is used to test the SpaceWire link or SWitty unidirectionally.

# 3.5 Summary

The basic function of the interface controller is to be a router that distributes packets coming in over a SpaceWire connection to the individual components of the low energy detector. This function has been nicely tucked away in two components, a receiver and a sender. For every component of the low energy detector, a control component has been developed when possible.

The interface controllers' design in Figure 3.2 has proven itself to work rather well. Simplicity and uniqueness of code and ideas throughout have contributed to its versatility. Simple debugging was achieved by creating all top-level components as equals, allowing each to be connected directly to the SpaceWire core. Beauty in logic and function in combination with equality, uniqueness, and simplicity has resulted in a highly modular design with great independence for every module. Multiple additional control components can be easily added. As a consequence, the interface controller has proven to be simple to use yet very versatile even in unforeseen situations such as a testing device for SWitty, the SpaceWire-to-USB converter described in chapter 5. As such, it will be interesting to see how the integration with the other components of the low energy detector of Simbol-X will go.

# Chapter 4

# The SpaceWire Protocol

A SpaceWire link is a full-duplex serial communication line capable of speeds of 2 Mbit/s up to 400 Mbit/s. The standard was spun off the IEEE 1355-1995 standard with the goal to make it suitable for space applications. The specification was first released on January 24, 2003 by the *European Cooperation for Space Standardization*, and it is now available under the designation ECSS-E-ST-50-12C(31 July 2008) at http://spacewire.esa.int[7].

It is already used in missions such as the Herschel space telescope launched in 2007 and the SWIFT space observatory launched in 2004. In the present context of Simbol-X, SpaceWire cables are used to connect the individual detector electronics to a common processing board known as the DPDPA. It is the purpose of the interface controller to provide the low energy detector of Simbol-X with a SpaceWire interface. In this chapter the SpaceWire protocol is described in some detail.

# 4.1 SpaceWire Basics

SpaceWire cables are specially shielded against electromagnetic interference. Since interference will most likely occur equally on all wires in the cable, only the difference between two signals is used. Such *differential signaling* is also standard in most serial communication protocols including the USB, Firewire, or Ethernet, although there are major differences in the electrical details. For SpaceWire, low voltage differential signaling (LVDS) is used, where the information is carried over the wire via a current that produces a low voltage signal across a  $100 \Omega$  resistor at the receiver. These electromagnetic interference counter measures result in a very reliable connection even at 60 Mbit/s as used in the laboratory.

Figure 4.1: SpaceWire connector contact identification viewed from rear of receptacle or front of plug. (adapted from Fig. 10, page 40 in ECSS-E-ST-50-12C[7])

SpaceWire is a fairly simple standard with a low footprint on electronic and energy resources. However, there is little guarantee for data integrity. A CRC8 field at the end of each packet was chosen for the Simbol-X mission to be able to detect data corruption and request resending of the data. This is sufficient for single bit errors.

The SpaceWire protocol also features what is called *time-codes*. These are data characters that take priority over normal data characters, and can be sent over a SpaceWire link at any time. With a relatively simple extension to the SpaceWire protocol proposed by F. Pinsard and C. Cara[14], time synchronization via time-codes can be achieved to an accuracy of up to two clock cycles. Although time-codes are not used at all for Simbol-X, they are mentioned here for completeness, and may be used in future space missions.

SpaceWire is a packet oriented protocol. A packet can be sent over a link only one at a time. To allow for smaller packets, SpaceWire encodes endof-packet characters efficiently as a 4-bit character, while normal characters are 10-bit with 8 bits of data. There is no start-of-packet character. The end of one packet marks the beginning of the next.

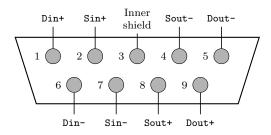

# 4.1.1 Basic Signals and Connectors

A SpaceWire link consists of 9 wires with micro-miniature connectors at each end. The connector identification is displayed in Figure 4.1.

There is an input and an output signal. The input signal is encoded using data-strobe, described in section 4.1.3, using a Din and an Sin signal. The Din and Sin signals are transmitted via LVDS, see section 4.1.2, giving Din+, Din-, Sin+, and Sin- signals. The same applies to the output signals, resulting in the signals Dout+, Dout-, Sout+, and Sout-.

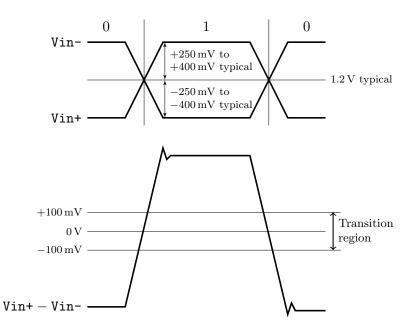

Figure 4.2: LVDS signaling levels. The above figure shows the absolute values of the voltage of the positive line Vin+ and the negative line Vinof a differential signal, and their swing around the 1.2 V value. The lower figure shows the difference between the two. A transition is detected when the difference is within 100 mV of 0 V. (adapted from Fig 3, page 29 in ECSS-E-ST-50-12C[7])

### 4.1.2 Low Voltage Differential Signaling

Low voltage differential signals are used for all signals because of their high immunity to induced noise. The voltage swing used here is typically  $\pm 350 \text{ mV}$ , although it can go from 250 to 400 mV, see Figure 4.2.

The transmitter provides a constant 3.5 mA current when there is a  $100 \Omega$  termination resistance on the other end. The receiver must have a high input impedance, so that most of the current flows through the termination resistor.

#### 4.1.3 Data Strobe Encoding

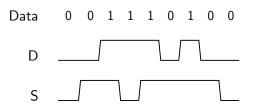

For each line there is a data signal D and a strobe signal S. The strobe signal changes whenever the data signal does not change, as shown in the example in Figure 4.3. In this way, only transitions need to be detected, resulting in an increased skew tolerance between the data and strobe signals. In case needed, the clock is reproduced by the XOR of the D and S signals.

Figure 4.3: Data Strobe (DS) encoding. The strobe signal S changes whenever the data signal D does not. (adapted from Fig 5, page 30 in ECSS-E-ST-50-12C[7])

The robustness of the data-strobe encoding has been tested by instantiating two cores in a single FPGA. Glitches were then inserted on the FPGAinternal D and S lines. There are two kinds of glitches that can be tested in this way. Either there is a bit flip in one of the signals, or there is a bit flip in both of them. As shown in the following, these errors are handled very well by the data-strobe encoding.

Let us first consider a bit flip on both lines, the D and the S line.

In dashed lines, the original example is shown, the solid line shows the signal with the glitch on both lines. This results in a signal that is still a valid data-strobe encoded signal, but with one bit flipped.

In general, if both the D and S lines flip, the transition will be on the other line, so the signal will remain valid, though with one bit flipped. One-bit flips are easily detected via the parity bit, described later in section 4.1.5.

The second kind of error is where only one of the lines flips. Let us consider the example where the D line flips one bit. This is the same situation as when the skew between the data and strobe signals becomes too large.

For a successful decoding it is essential to determine the order of transitions. The SpaceWire core must determine which signal transition is occurring before the other. In the extreme case discussed here, two transitions are occurring at the same time, with differences introduced by jitter inside the

#### 4.1. SPACEWIRE BASICS

FPGA. The SpaceWire receiver must tolerate this and can randomly choose which is first.

The dashed signal shows the original data signal in the figure above. Should the actual transition occur after the transition in the strobe signal, or be detected as such, then the bit marked 'X' will be a 0. This error is once again detectable via the parity bit.

Should the actual transition occur slightly before the transition in the strobe signal, then 'X' is 1, and there is no error.

This epitomizes the extraordinary skew and jitter tolerance that the datastrobe encoding brings to the SpaceWire protocol.

# 4.1.4 Characters and Control Codes

The SpaceWire protocol is a packet oriented protocol, and it uses a special character encoding for marking the end-of-packet or error-end-of-packet characters.

A character consists of either 4 or 10 bits. The first two bits in a character are always the parity bit and the control flag. The parity bit is used to detect single bit errors, and it is set as described in Section 4.1.5. The control flag determines whether the character is a data character or a control character.

When the control flag is 0, then the character is a data character, and the next 8 bits contain the data, LSB first.

If the control flag is 1, then the character is a control character, and the next 2 bits indicate whether it is an FCT (flow control token), EOP (end of packet), EEP (error end of packet), or ESC (escape) character.

In addition, the SpaceWire protocol recognizes combinations of characters, called *control codes*. There are two control codes, NULLs and Time-Codes. A NULL is also called a NULL-*character*. It is formed from an ESC character followed by an FCT. A time code is formed from an ESC, followed by a data character.

Figure 4.4 illustrates the individual character types and control codes. Data characters, EOP, and EEP characters are also called normal characters, or N-Chars. ESC, FCT, NULL-characters, and time-codes are also called link characters, or L-Chars.

### 4.1.5 The Parity Bit

The purpose of the parity bit is to detect simple 1-bit errors. It is set such that the total number of 1's in the covered field is always odd.

| Data characters                                        |

|--------------------------------------------------------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| $\uparrow$ LSB MSB                                     |

| Control flag                                           |

| C Parity bit                                           |

| Control characters                                     |

| P 1 0 0 FCT Flow control token                         |

| P 1 0 1 EOP Normal end of packet                       |

| P 1 1 0 EEP Error end of packet                        |

| P 1 1 1 ESC Escape                                     |

| Control codes                                          |

| P 1 1 1 0 1 0 0 NULL                                   |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

Figure 4.4: Data characters, control characters, the null character, and time codes. (adapted from Fig 6, page 31 in ECSS-E-ST-50-12C[7])

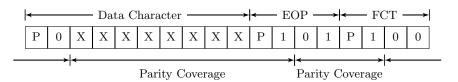

Figure 4.5: Parity coverage. As an example, the sequence of a data character followed by an EOP and an FCT is shown. The parity bits are set such that the number of 1's in the parity coverage is odd. The figure illustrates that the parity coverage includes the end of the previous character and the beginning of the current character. (adapted from Fig 17, page 53 in ECSS-E-ST-50-12C[7])

The parity bit covers the following bits: itself, the control flag, and the last 8 bits of the previous data character or the last 2 bits if the previous character was a control character. Figure 4.5 illustrates the coverage of the parity bit.

### 4.1.6 Packets

A packet is formed by one or more data characters followed by either EOP or EEP. An EEP indicates the end of a packet in which an error occurred.

Characters from two different packets may not be interleaved. Only FCTs, NULLs, and Time-Codes can be interleaved with a packet. The data character immediately following an EOP or EEP is the first character of the next

Figure 4.6: SpaceWire Link Interface State Machine. In normal operation, the link interface follows the thick arrows into the Run state. On error it transitions back to the ErrorReset state, from where it will restart the link establishing sequence until it reaches the Run state. See section 4.2 for details. (adapted from Fig 20, page 60 in ECSS-E-ST-50-12C[7])

packet. When an error occurs, the packet needs to be closed either with an EOP or EEP before sending new data characters.

In a network setting, the first data characters are to be interpreted as destination addresses, and thus stripped one after the next as the packet passes through the network.

# 4.2 Establishing a SpaceWire Link

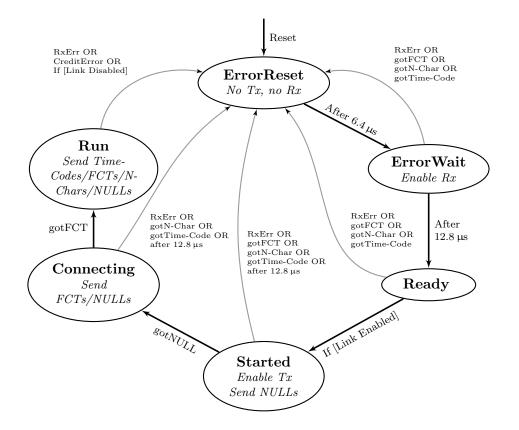

Figure 4.6 displays a typical state machine of a SpaceWire link interface component such as the one used in this work. The following sequence of events lead to a successful SpaceWire link.

1. The link interface component starts out in the *ErrorReset* state. This state is also entered on every reset of the component, and whenever an error in the transmission occurs.

In the *ErrorReset* state both the receiver Rx and the transmitter Tx are disabled.

2. After 6.4  $\mu$ s the link component will transition to the *ErrorWait* state where the receiver is enabled. The component will stay in this state for 12.8  $\mu$ s, and then enter the *Ready* state.

These timeouts are used for ensuring a successful "exchange of silence", explained in section 4.2.3, in case an error occurred.

3. The specific SpaceWire link component used in this work publishes multiple input signals to give a fine-grained control on the link connecting behavior. It may be configured as "link enabled", "link disabled" or "automatic". In the simplest case, the component is enabled and will simply transition to the *Started* state and start the connection.

Alternatively, the link may be disabled. In this case, the component will stay in the *Ready* state until the configuration changes or an error occurrs.

In automatic mode, the link will only transition to the *Started* state when it detects that a connection attempt is made by the other side of the link. This is the case when the receiver detects a NULL-character.

Automatic mode is what is used in the interface controller. That way it is up to the DPDPA in the rest of the spacecraft to enable or disable the nominal interface controller or the redundant one.

- 4. In the *Started* state, the link interface component enables the transmitter and sends out a continuous stream of NULL-characters to inform the other side of its existence.

- 5. Each side of the link can now detect a NULL-character from the opposite side. This tells each link component that the link is working and they can each enter the *Connecting* state.

- 6. Now the link is essentially established, and the two ends of the link inform each other how much room they have for receiving characters. This is done via flow control tokens (FCT) as described in the next section.

- 7. Upon detection of at least one FCT, each side can finally enter the Run state for normal operation.

48

## 4.2.1 Flow Control

The SpaceWire protocol ensures proper flow control of data characters. That is, each side of a SpaceWire link needs to keep track of how much space the other side has left for receiving characters. The maximum is to have room for 56 bytes of data, the minimum is 8 bytes. The maximum ensures that a 6-bit number is sufficient for keeping track. The minimum comes from the fact that each sending of an FCT implies that the sending side has room for receiving 8 more bytes. In this way, each side of the link knows exactly how many normal characters it is allowed to send across the link before receiving another FCT.

A *CreditError* occurrs when either too many normal characters or more than 7 FCTs corresponding to the maximum of 56 bytes have been received. If a *CreditError* occurrs, the link needs to be re-established.

# 4.2.2 The Run State

The *Run* state is the state of normal operation. In this state all kinds of characters can be sent from NULL-characters, normal characters, flow control tokens, and times-codes. These characters are sent with different priorities to ensure a smooth operation, as follows.

- NULL-characters are sent with the lowest priority. They are always sent if nothing else is pending in order to keep the link active and prevent the other side from detecting an exchange of silence.

- Of slightly higher priority are normal characters. These represent the data requested by the application. If the application indicates one should be sent, the link component waits for the current character to finish being sent and then immediately afterwards sends the normal data character.

- The second highest priority goes to flow control tokens. These must have a higher priority than normal characters, so that the receiving line is not drowned out by the sending line.

- In the *Run* state, time-codes are sent with the highest priority. They are not buffered and so do not need any form of flow control.

In any case, before sending a character, the link component waits for the current character to finish.

Initially, the clock frequency on the link must be  $10 \pm 1$  MHz. During the *Run* state, the component may change to a different speed, where the lowest

is 2 MHz, and the highest is determined by skew, jitter, and the capabilities of the two ends of the link. The minimum speed is set since it counts as a disconnect error when neither the data nor the strobe signal changes within 850 ns. The SpaceWire core used in this work adjusts the clock speed automatically once in the Run state.

### 4.2.3 Link-Level Error Notification: The Exchange of Silence

There are three kinds of link-level errors that result in an "exchange of silence", although by some countings these are five errors:

- An *RxError* occurrs when either a disconnect was detected, a parity error occurred, or an escape error occurred.

- A disconnect error is detected when there is a transition on neither the data nor the strobe signal for at least 850 ns.

- A parity error occurrs when the number of bits in the parity coverage is not odd.

- An escape error occurrs whenever an ESC character is followed by an invalid character, that is, it is neither followed by an FCT resulting in a NULL nor by a data character resulting in a timecode.

- A character sequence error occurrs whenever an unexpected character is received during link initialization, for instance, when an FCT is received before a NULL has been sent.

- Also, *CreditErrors* as described in the flow control section 4.2.1 belong to the category of link level errors.

The two ends of the link notify each other of such link errors by an "exchange of silence". The side of the link detecting the error transitions to the *ErrorReset* state, thus causing a disconnect error on the other end of the link. Both sides then cycle through the link initialization procedure, during the first  $19.2 \,\mu$ s of which no signal is transmitted.

Should one end have not correctly detected the disconnect, then the other side will cycle between the *ErrorReset* and *ErrorWait* states during which it transmits no signal. This exchange of silence ensures that a disconnect error is certainly detected on both ends.

Table 4.1: Transmitter and receiver host data interface encoding. (adapted from Table 7, page 54 in ECSS-E-ST-50-12C[7])

| Control flag | Data bits (MSB LSB)    | Meaning    |

|--------------|------------------------|------------|

| 0            | XXXXXXXX               | 8-bit data |

| 1            | xxxxxx0 (use 00000000) | EOP        |

| 1            | xxxxxx1 (use 00000001) | EEP        |

# 4.3 Application Side Interface

Although the standard does not mandate that implementations of the Space-Wire protocol follow the same application side interface specification, the recommendation summarized here is followed by at least two SpaceWire cores, including the one used for Simbol-X.

Only normal characters (data, EOP, and EEP characters) are exchanged with the application. Such characters between the link interface and the host application contain 9 bits. The first bit is the control flag, as indicated in Table 4.1. When the control flag is 1, the bits marked 'x' are ignored, but should be set to 0. If the control flag is 0, the other 8 bits contain the data. Also, link-level errors are reported via at least one signal, **RxError**.

# 4.4 Conclusion

SpaceWire is an easy to use high-speed point-to-point serial communication link with a low resource usage. A SpaceWire VHDL component synthesized completely inside an FPGA is quick to setup, allowing the developer to concentrate on other issues.

SpaceWire has been explicitly designed to be used in space applications, featuring very good immunity to electromagnetic interference. Speeds of 2 Mbit/s up to 400 Mbit/s are possible.

The overhead introduced by the SpaceWire protocol is 2 bits per byte. At a signaling frequency of 20 MHz as envisioned for Simbol-X, this allows a maximum data rate of 2 MB/s, well above the expected maximum of about half a megabyte per second.

As a standard, the SpaceWire protocol provides for seamless integration of satellite components developed around the world. The fairly clean application side interface allows a SpaceWire VHDL core to be reused in many components as well as in future missions. 52

# Chapter 5

# The SpaceWire-to-USB Converter SWitty

In this chapter SWitty is described. SWitty is a SpaceWire-to-USB converter to easily connect the interface controller or any other SpaceWire cable to a computer. The main component is a VHDL USB core that has a much more general application as a cheap method for transferring large amounts of data between hardware and software.