# Entwicklung einer USB-Schnittstelle für die Ausleseelektronik eines

# Cadmium-Zink-Tellurid Detektors

Diplomarbeit

von

Giuseppe Distratis

Eberhard Karls Universität Tübingen Fakultät für Mathematik und Physik Institut für Astronomie und Astrophysik Abteilung Astronomie

Mai 2006

## Inhaltsverzeichnis

| 1 | Einf | ührung                               | 1  |

|---|------|--------------------------------------|----|

|   | 1.1  | Motivation und Inhalt dieser Arbeit  | 2  |

|   | 1.2  | MIRAX                                | 2  |

|   |      | 1.2.1 Hard X-ray Imager              | 3  |

|   |      | 1.2.2 CdZnTe-Detektor                | 4  |

|   |      | 1.2.3 Labor-Prototyp                 | 4  |

| 2 | Aus  | leseelektronik                       | 7  |

|   | 2.1  | Allgemeines Design                   | 8  |

|   |      | 2.1.1 Zeitstempel                    | 12 |

|   | 2.2  | Datenverkehr auf dem Bus             | 14 |

|   |      | 2.2.1 Datenformat                    | 15 |

|   | 2.3  | Leistungsgrenzen                     | 17 |

| 3 | REN  | NA Control Interface                 | 19 |

|   | 3.1  | "Swatter"                            | 20 |

|   | 3.2  | Eingesetztes USB-Modul               | 22 |

|   | 3.3  | RCI-Versorgungsplatine               | 23 |

|   |      | 3.3.1 Stromversorgung                | 23 |

|   |      | 3.3.2 LVDS-Bustreiber                | 25 |

|   |      | 3.3.3 Weitere Anschlüsse             | 26 |

| 4 | VHI  | DL-Design - Aufbau                   | 29 |

|   | 4.1  | Funktionsprinzip                     | 30 |

|   | 4.2  | Datenformate                         | 33 |

| 5 | VHI  | DL-Design - Detaillierte Darstellung | 35 |

|   | 5.1  | Top-Level-Modul                      | 35 |

|   | 5.2  | RENA-Befehlsschnittstelle            | 36 |

|   |      | 5.2.1 Erweiterung der Zeitstempel    | 37 |

|   | 5.3  | Auslese-Sequenzer                    | 38 |

|   |      | 5.3.1 Synchronisation der Boards     | 38 |

|   | 5.4  | RENA-Konfiguration                   | 39 |

|   | 5.5  | Kommunikationsschnittstelle          | 40 |

|   | 5.6  | Testumgebung                         | 42 |

|   |      | 5.6.1 Leistung der Datenübertragung  | 42 |

iv Inhaltsverzeichnis

| 6   | Aus   | blick                                          | 47           |

|-----|-------|------------------------------------------------|--------------|

| Α   |       | d-Programmable Gate Array Hardwaremodellierung | <b>49</b> 50 |

| В   |       | versal Serial Bus                              | 53           |

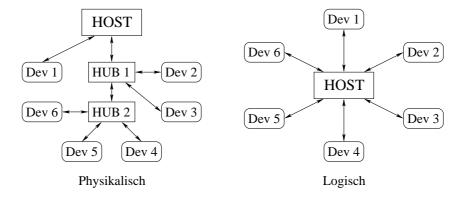

|     | B.1   | Kommunikationsmodell                           | 53           |

|     |       | B.1.1 Transferarten                            | 55           |

|     | B.2   | Topologie                                      | 56           |

|     | B.3   | Funktionsprinzip                               | 57           |

|     |       | B.3.1 Elektrische Buszustände                  | 58           |

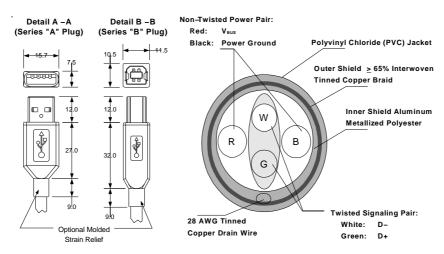

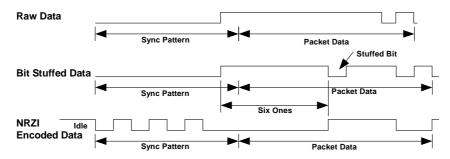

|     |       | B.3.2 Datenkodierung                           | 59           |

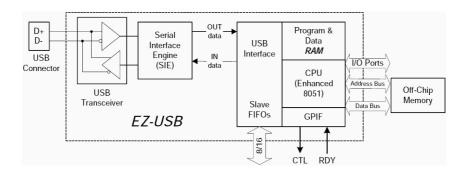

|     | B.4   | Implementierung von Cypress                    | 60           |

| C   | Abk   | ürzungen und Akronyme                          | 63           |

| Lit | eratı | ırverzeichnis                                  | 65           |

# **Tabellenverzeichnis**

| 2.1 | Belegung des RENA-Buskabels | 12 |

|-----|-----------------------------|----|

| 2.2 | RENA-Befehle                | 16 |

| 2.3 | Format des HIT-Datensatzes  | 17 |

| 4.1 | RCI-Befehle                 | 32 |

| 4.2 | RCI-Datenpakete             | 33 |

| 4.3 | Datenformate                | 34 |

| B 1 | USB PIDs                    | 55 |

vi Tabellenverzeichnis

# Abbildungsverzeichnis

| 1.1 | Logo der MIRAX-Mission             | 3  |

|-----|------------------------------------|----|

| 1.2 | HXI-Teleskop                       | 4  |

| 1.3 | Elektrodenanordnung                | 5  |

| 1.4 | HXI-Detektor                       | 5  |

| 1.5 | CdZnTe-Detektor, Prototyp          | 6  |

| 2.1 | RENA-Hybrid                        | 7  |

| 2.2 | RENA-Chip: Analogpfad              | 8  |

| 2.3 | RENA-Chip: Blockschaltbild         | 9  |

| 2.4 | RENA Module Board                  | 10 |

| 2.5 | RENA System Interface              | 13 |

| 2.6 | Struktur des Datenpakets           | 14 |

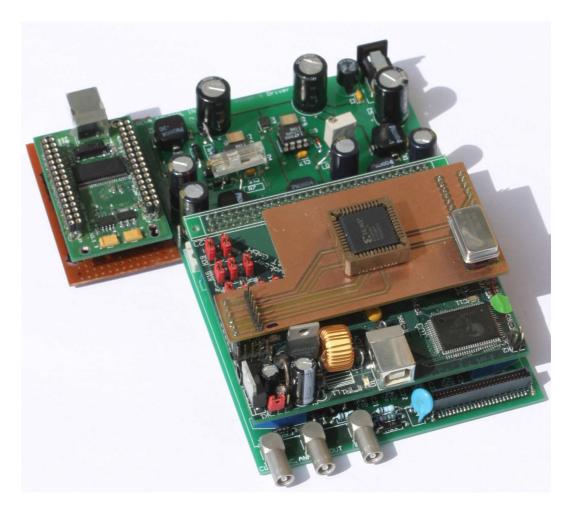

| 3.1 | Swatter                            | 21 |

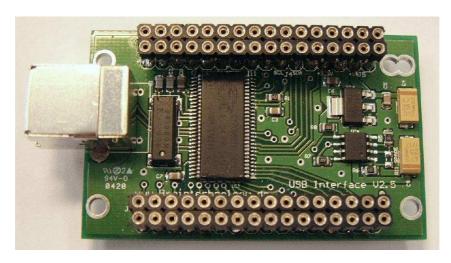

| 3.2 | USB-Modul                          | 23 |

| 3.3 | Schaltplan                         | 24 |

| 3.4 | USB-Zwischenlösung                 | 26 |

| 3.5 | Hauptplatine                       | 27 |

| 4.1 | Blockdiagramm                      | 29 |

| 4.2 | Flussdiagramm der der RCI-Befehle  | 31 |

| 5.1 | Top-Level des RCI-Designs          | 44 |

| 5.2 | Problematische Zeitstempel         | 45 |

| 5.3 | Konfiguration, Waveform            | 45 |

| 5.4 | Kommunikation, Waveform            | 45 |

| 6.1 | RCI, komplett aufgebauter Prototyp | 48 |

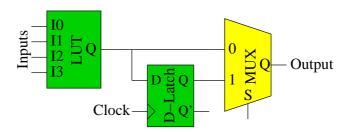

| A.1 | Configurable Logic Block           | 50 |

| A.2 | HDL-Modellierung                   | 52 |

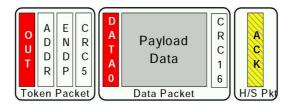

| B.1 | USB Pakete                         | 54 |

| B.2 | USB Topologie                      | 56 |

| B.3 | USB Stecker und Kabel              | 57 |

| B.4 | NRZI-Kodierung                     | 59 |

| B 5 | Bit-Stuffing                       | 59 |

| viii |                    | Abbildungsverzeich | nis |

|------|--------------------|--------------------|-----|

|      |                    |                    |     |

| B.6  | EZ-USB Blockschema |                    | 61  |

## Kapitel 1

## Einführung

Die Röntgenastronomie ist noch ein relativ junges Kapitel in der Geschichte der Astronomie. Es ist kaum mehr als ein halbes Jahrhundert her, als Thomas Burnight mit einem Detektor auf einer umgebauten V2-Rakete erstmals die Röntgenstrahlen der Sonnenkorona beobachtete.

Da Röntgenstrahlen vollständig von der Erdatmosphäre absorbiert werden, ist eine Beobachtung nur aus sehr großer Höhe bzw. aus dem Weltall möglich. Dies stellte natürlich eine Hürde dar, was vielleicht erklären kann, warum erst vierzehn Jahre nach dem ersten Experiment von Burnight Riccardo Giacconi mit einer Höhenforschungsrakete, die mit einem Röntgendetektor ausgestattet war, zwar nicht die beabsichtigte Röntgenaufnahme des Mondes, jedoch die Entdeckung der ersten kosmischen Röntgenquelle Scorpius X-1 gelang. Danach ging es auf diesem Gebiet zwar nicht sehr schnell, aber stetig voran. Zuerst wurden für die Beobachtung noch Raketen und Ballone benutzt, später Satelliten. Durch die technischen Entwicklungen in diesem Bereich konnten immer mehr kosmische Röntgenquellen entdeckt werden. Mit den empfindlichen Instrumenten an Bord des ROSAT-Satelliten gelang es in den 90er Jahren, mehr als 100 000 Röntgenquellen zu entdecken und nebenbei auch Giacconis ursprüngliches Vorhaben zu verwirklichen – eine Röntgenaufnahme des Mondes.

Das Institut für Astronomie und Astrophysik der Universität Tübingen (IAAT) engagiert sich bereits seit über 40 Jahren auf diesem Gebiet. Schon in den 1960ern wurden Kameras zur Beobachtung der Röntgenstrahlung der Sonne entwickelt und Anfang der 70ern unter der Leitung von Herrn Professor Joachim Trümper, der die Röntgenastronomie in Tübingen vorantrieb, wurden eigene Ballonexperimente durchgeführt. Herr Professor Rüdiger Staubert führte die Forschung in diesem Bereich fort mit der Beteiligung an vielen Satellitenprojekten u.a. mit dem bereits erwähnten, erfolgreichen ROSAT-Projekt sowie XMM-Newton und INTEGRAL, die noch aktiv sind. Als Nachfolger betreibt heute Herr Professor Andrea Santangelo die Weiterführung dieser Forschung u.a. mit der Beteiligung an den aktuellen Projekten SIMBOL-X, eROSITA und MIRAX.

#### 1.1 Motivation und Inhalt dieser Arbeit

Gegenstand dieser Arbeit war die Entwicklung einer Schnittstelle für das Auslesen der Daten eines Röntgenteleskops, das sich an Bord des MIRAX-Satelliten befinden wird. Aus diesem Grund werden der Satellit, das Teleskop und der dafür eingesetze Detektor im folgenden Abschnitt kurz vorgestellt. Dieses Teleskop (siehe Abschnitt 1.2.1) wird derzeit am Center for Astrophysics & Space Sciences der Universität von Kalifornien in San Diego, USA (CASS/UCSD) entwickelt.

Es soll hier jedoch nicht der Eindruck erweckt werden, es würde sich bei dieser Schnittstelle um einen Teil der Bordelektronik handeln. Es ist vielmehr der erste Schritt in diese Richtung, mit der Hoffnung, das IAAT bei der Aufgabe, die es für das MIRAX-Projekt übernommen hat, ein kleines Stück voranzubringen.

Kapitel 2 befasst sich eingehend mit der Elektronik für das Auslesen des Detektors. Sie stellt den Ausgangspunkt dar für die Entwicklung, die in den Kapiteln 4 und 5 ausführlich beschrieben wird. Die Anhänge A und B sind kurze Einführungen in die für diese Entwicklung eingesetzten Technologien.

Abkürzungen und Akronyme, die im Laufe dieser Arbeit benutzt werden, sind bei ihrer ersten Verwendung auch im Klartext aufgeführt, kommen sie mehr als einmal im Text vor, ist es möglich, sie im Anhang C nachzuschlagen. <sup>1</sup>

#### 1.2 MIRAX

Monitor et Imageador de RAios-X (MIRAX) ist der Name eines Kleinsatelliten der gemeinsam vom Brasilianischen Instituto Nacional de Pesquisas Espaciais (INPE), der Space Research Organisation Netherlands (SRON), dem Massachussetts Institute of Technology (MIT), der University of Warwick in Großbritannien sowie dem CASS/UCSD und dem IAAT entwickelt wird. Das IAAT steuert mit der Central Electronics Unit (CEU) die zentrale elektronische Steuereinheit bei und ist an der Entwicklung der Auswertungssoftware beteiligt.

Wissenschaftliches Ziel dieser Mission ist die Langzeitbeobachtung der galaktischen Ebene und insbesondere deren Zentralregion, im Energiebereich von  $2-200\,\mathrm{keV}$  mit sehr hoher Zeitauflösung von  $10\,\mu\mathrm{s}$  [SR<sup>+</sup>03].

Wegen der Nähe der Sonne zur galaktischen Zentralregion im Laufe eines Erdorbits, ist ihre Beobachtung nicht ununterbrochen möglich. Für drei Monate im Jahr sollen deshalb andere interessante Regionen wie Crab oder Vela beobachtet werden.

<sup>&</sup>lt;sup>1</sup>Oft sind Begriffe der Elektronik besser unter deren Akronym bekannt als in Klarschrift. Um den Wiedererkennungswert dieser Kürzeln auszunutzen, werden sie auch dort eingesetzt, wo sie vielleicht nicht nötig gewesen wären.

Abbildung 1.1: Offizielles Logo der MIRAX-Mission

An Bord von MIRAX werden sich drei Coded-Mask-Röntgenteleskope befinden. Bei einem davon, dem Soft X-ray Imager (SXI), handelt es sich um das Ersatzexemplar der Wide Field Camera des sehr erfolgreichen italienisch/niederländischen Satelliten BeppoSAX. Es ist mit einem Vieldrahtproportionalzähler, empfindlich im Energiebereich von  $2-28\,\mathrm{keV}$  ausgerüstet und besitzt ein Gesichtsfeld von  $20^\circ\times20^\circ$ . Die zwei identischen Hard X-ray Imager Teleskope (HXI) überdecken zusammen einen Himmelsausschnitt von  $45,8^\circ\times22,9^\circ$  und sind im Energiebereich von  $10-200\,\mathrm{keV}$  empfindlich.

#### 1.2.1 Hard X-ray Imager

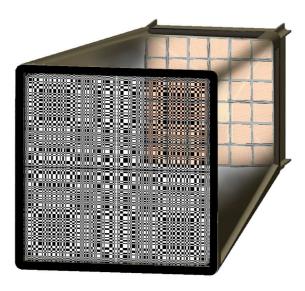

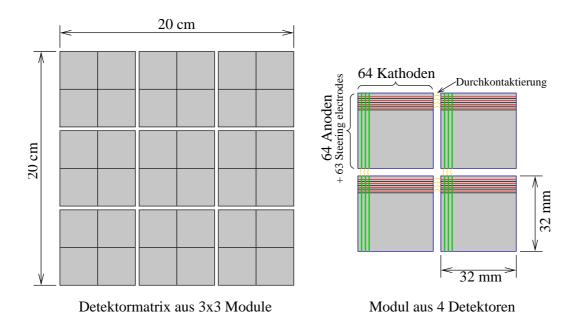

Der HXI ist der Beitrag vom CASS/UCSD an dem MIRAX-Projekt [R<sup>+</sup>03]. Es handelt sich um ein Coded-Mask-Teleskop mit einer Wolframmaske von 0,6 mm Dicke, gebildet aus  $157 \times 157$  Zellen in Modified Uniformly Redundant Array (MURA) Anordnung. Die Abschattung der Maske beträgt 50%. Im Abstand von 76 cm hinter der Maske befindet sich eine Matrix aus  $3 \times 3$  Crossed-Strip-Detektormodulen mit einer Gesamtfläche von ca.  $360 \, \mathrm{cm}^2$  (s. Abb. 1.2). Die Detektormodule bestehen ihrerseits aus einer Matrix aus  $2 \times 2$  CdZnTe-Detektoren von  $32 \times 32 \times 2 \mathrm{mm}^2$ . Die je 64 Anoden und Kathoden der 4 Einzeldetektoren sind so miteinander verbunden, dass das Modul als ein  $128 \times 128$ -Pixel großer Detektor angesteuert werden kann.

Abbildung 1.2: Aufbau des Hard X-ray Imagers [SR<sup>+</sup>03]

#### 1.2.2 CdZnTe-Detektor

Cadmium-Zink-Tellurid-Detektoren zeichnen sich durch gute Effizienz und Energieauflösung sowie sehr niedriges thermisches Rauschen bei Raumtemperatur aus. Die ausgezeichnete Ansprechzeit dieser Art von Detektoren erlauben ihren Einsatz in Anwendungen wie MIRAX.

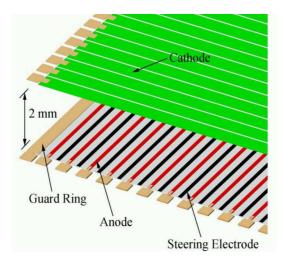

Die bei MIRAX einzusetzenden Detektoren weisen zwischen den Anodenstreifen zusätzliche s.g. Steering Electrodes auf. Sie werden mit einer Vorspannung (Bias) angesteuert, die bei etwa 90% der Biasspannung zwischen Anoden und Kathoden (130 – 200 V) liegt. Die Steering Electrodes tragen zur Verbesserung der Ladungssammeleigenschaft des Detektors bei [ $R^+03$ ; KM00;  $S^+00$ ].

#### 1.2.3 Labor-Prototyp

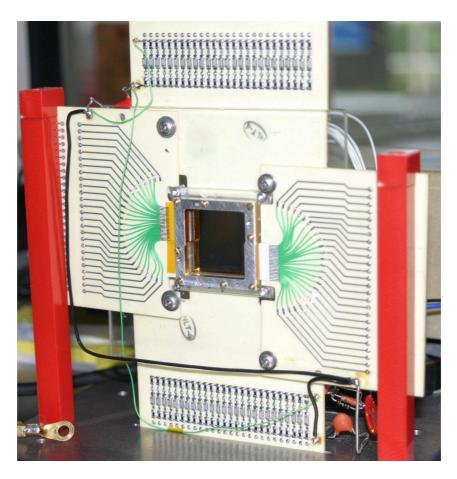

Der dem IAAT zur Verfügung stehende CdZnTe-Detektor (siehe Abbildung 1.5) ist ein sehr früher Prototyp, welcher auf einem Splayed-Out-Board montiert ist. Dieses Board erlaubt durch die weit aufgefächerten Anschlüsse zwar einen schnellen Zugriff auf die einzelnen Elektroden, hat aber den Nachteil einer sehr großen Empfindlichkeit für elektromagnetische und sogar akustische Störungen. Zur Zeit wird am IAAT ein sehr kompakter Träger für den Detektor konstruiert, um diese Probleme wesentlich zu verringern.

**Abbildung 1.3:** Elektrodenanordnung des CdZnTe-Detektors[S $^+00$ ]

${\bf Abbildung}$  1.4: Aufbau des HXI-Detektor

Der Detektor ist aus 9 einzelnen Modulen aufgebaut. Jedes Modul besteht aus 4 CdZnTe-Crossed-Strip-Detektoren mit 64 Kathoden und 64 Anoden, die zwischen benachbarten Detektoren durchkontaktiert werden. Es entsteht auf dieser Weise einen Gitter aus  $128 \times 128$  Elektroden, deren Kreuzungspunkte eine ebenso große Matrix von Bildpunkten (Pixels) bildet. Die Steering electrodes werden auf die gleiche Weise durchkontaktiert. Dies wird im Bild aus Gründen der Übersichtlichkeit nicht gezeigt.

Abbildung 1.5: Prototyp des CdZnTe-Detektors am IAAT

Das Bild zeigt die Kathodenseite. Die Anschlüsse der Elektroden sind zu je einer Hälfte rechts, bzw. links des Detektors durch kleine Drähte mit den Leiterbahnen des Splayed-Out-Boards verbunden. Jede Kathode ist über einen Widerstand von  $1\,\mathrm{G}\Omega$  mit der Masse verbunden. Das Signal wird direkt an dem Widerstand abgegriffen. Auf der Rückseite befinden sich die Anoden. Sie sind senkrecht zu den Kathoden angeordnet und ebenfalls über  $1\,\mathrm{G}\Omega$  Widerstände auf der Bias-Spannung gehalten. Um die Ausleseelektronik nicht mit dieser hohe Spannung zu verbinden, werden die Signale durch Entkopplungskondensatoren geleitet.

## Kapitel 2

## Ausleseelektronik

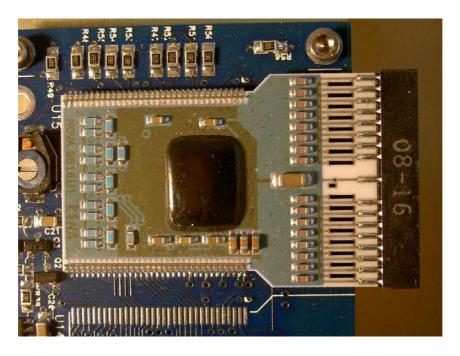

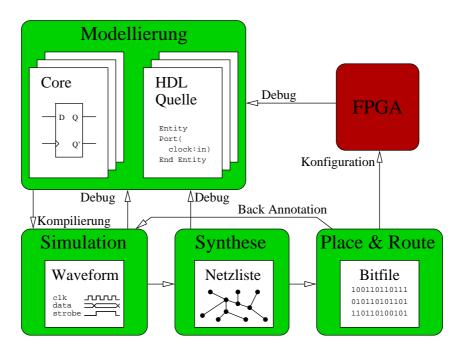

Abbildung 2.1: RENA-Chip auf der Hybrid-Platine

Das Readout Electronics for Nuclear Applications (RENA) Auslesesystem der Firma NOVA R&D Inc. in Riverside, Kalifornien ist speziell für den Betrieb mit hochkapazitiven Halbleiterdetektoren im Bereich von 6 bis 50 pF konzipiert. Es zeichnet sich durch eine hohe Flexibilität und Empfindlichkeit aus und erlaubt den Einsatz von Detektoren aus Silizium, Cadmium-Tellurid, Cadmium-Zink-Tellurid, Quecksilber-Jodid und Gallium-Arsenid. Die hohe Anzahl unabhängiger und einzeln triggerfähiger Eingangskanäle macht es für die Auslese von Crossed-Strip-Detektoren wie dem CdZnTe-Detektor der HXIs besonders geeignet [MTK<sup>+</sup>98].

#### 2.1 Allgemeines Design

Die Hauptkomponente der *RENA* ist der s.g. *RENA*-Chip, eine *kundenspezifische* integrierte Schaltung (ASIC<sup>1</sup>) die auf einer Hybrid-Platine<sup>2</sup> montiert ist.

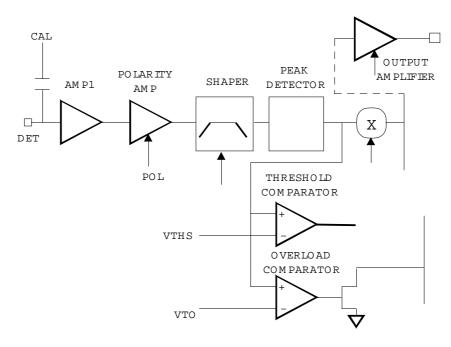

**Abbildung 2.2:** Analogpfad eines Eingangskanals [MTK<sup>+</sup>98]

In jedem seiner 32 Eingangskanäle erzeugt ein integrierender Ladungsverstärker einen Spannungspuls, dessen Energie proportional zur Ladung ist, welche von der angeschlossenen Detektorelektrode gesammelt wird (s. Abb. 2.2). Die von einem Photon im Detektor erzeugte Ladung kann von bis zu je drei benachbarten Kathoden und Anoden gesammelt werden. Ist der Kanal an einer Anode angeschlossen, muss die Polarität des Signals durch einen Polaritätsverstärker invertiert werden, bevor es durch den digitalgesteuerten Pulsfilter und Peak-Detektor weiter verarbeitet und über einen Multiplexer (der mit "X" gekennzeichnete Kreis in Abb. 2.2) zum Ausgangsverstärker geführt wird. Zwei Komparatoren vergleichen die Spannung des Signals mit den digital eingestellten Trigger- bzw. Überladungspegeln.

Das Triggersignal am Ausgang des Schwellenkomparators steuert zusätzlich die digitale Adress-Logik.

<sup>&</sup>lt;sup>1</sup>Application Specific Integrated Circuit.

<sup>&</sup>lt;sup>2</sup>Engl., vom Lat. *hybris*: Zwitterwesen. Als *Hybrids* werden in der Elektronik Tochterplatinen bezeichnet, die wie Bauteile auf einer Mutterplatine verwendet werden (s. Abb. 2.1).

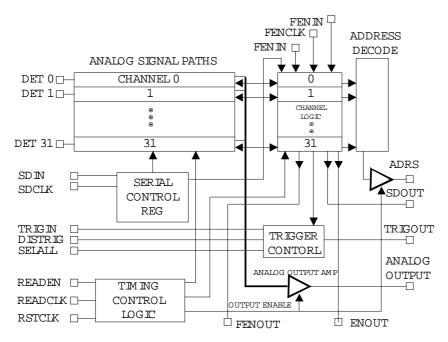

Die Konfigurationsdaten der digitalgesteuerten analogen Komponenten werden in zwei Schieberegister des RENA-Chip geschrieben (s. Abb. 2.3). Die in einem weiteren Register gespeicherte Information bestimmt welches Analogsignal zu Überwachungszwecken an einen Ausgangsverstärker geleitet wird. Die Ein- und Ausgangsleitungen der Schieberegister werden über alle Hybrids eines Moduls kaskadiert, so dass von aussen nur je ein Register sichtbar ist, dessen Breite von der Anzahl der auf dem Board installierten Hybrids abhängt.

Abbildung 2.3: Blockschaltbild des RENA-Chips

Das Serial Control Register enthält die Konfigurationsdaten der digitalgesteuerten analogen Komponenten. Das Force-Enable (FEN) Register ist in die Adress-Logik integriert und bestimmt welcher Kanal dauerhaft am Analogausgang zur Überwachung bereitsteht [MTK<sup>+</sup>98].

Der *RENA*-Chip ist so konstruiert, dass bis zu 4 Hybrids auf einem *RENA Module Board* installiert werden können (s. Abb. 2.4) und sich sowohl einen digitalen Adress-Bus als auch einen analogen Ausgangsbus teilen, während die Steuerleitungen in einer *Daisy-Chain*<sup>3</sup> kaskadiert werden. Dadurch ist nur genau ein Befehl notwendig um die Register aller Hybrids zu konfigurieren.

Ein Digital-Analog-Wandler (DAC<sup>4</sup>) mit vier Kanälen vom Typ MAXIM MAX525 erzeugt die Referenzspannungen VTHS und VTO. Ein 14-Bit Analog-Digital-Wandler (ADC<sup>5</sup>) vom Typ Analog Devices AD9243 sorgt für die Digitalisierung der ge-

<sup>&</sup>lt;sup>3</sup>Eine Kette von gleichen elektronischen Komponenten, bei der die Ausgänge des ersten Glieds direkt mit den Eingängen des zweiten Glieds verbunden sind usw.

<sup>&</sup>lt;sup>4</sup>Digital to Analog Converter

<sup>&</sup>lt;sup>5</sup>Analog to Digital Converter

Abbildung 2.4: Das RENA Module Board des IAAT

Von vier möglichen *RENA*-Hybrids sind nur zwei installiert, auf den Positionen 2 und 0 (von links nach rechts). Da bei dieser Version des Boards die Einstellung der Polaritätsverstärker nicht für jeden einzelnen Kanal getrennt erfolgen kann, sondern nur paarweise für die Chips 0 und 1 bzw. 2 und 3, ist es nur mit dieser Minimalkonfiguration möglich, sowohl die Anoden als auch die Kathoden des Detektors auszulesen.

#### messenen Ladungsmenge.

Auf dem Board befindet sich noch ein Field-Programmable Gate Array (FPGA<sup>6</sup>) vom Typ Spartan XCS20 der Firma XILINX. Das FPGA stellt zwei weitere Schieberegister zur Verfügung: das DAC-Register für die Kontrolle der Referenzspannungen und das Control and Status Register (CSR), das alle für den Betrieb des RENA Module Boards notwendigen Parameter enthält. Dieses FPGA steuert die Hybrids, die Erzeugung der Kalibrationspulse und die Kommunikation mit der Steuer- und Kommunikationsschnittstelle, dem RENA System Interface.

Die RENA Module Boards werden über ein 50-poliges Hochdichte-Flachbandkabel an das RENA System Interface angeschlossen. Obwohl das Interface bis zu 16 Boards adressieren kann, sind seine Stromversorgungskomponenten so dimensioniert, dass nur 8 Boards mit den nötigen Betriebsspannungen versorgt werden können.

Für die Kommunikation mit dem Datenerfassungscomputer wird das Interface über

<sup>&</sup>lt;sup>6</sup>Auf FPGAs, ihre Eigenschaften und Arbeitsweise wird im Anhang A näher eingegangen.

ein weiteres 50-poliges Flachbandkabel an einer PCI-Schittstelle<sup>7</sup> vom Typ National Instruments DIO-96 angeschlossen.

Die einzelnen Boards werden durch ihre Identifikationsnummer (ID), die an einer Jumper-Leiste als binär codiert wird, unterschieden. Die Nummerierung muss bei Null beginnen und lückenlos bis zur Anzahl der angeschlossenen Boards minus eins gehen. Der Datenbus wird auf einer Seite durch das RENA System Interface terminiert. Die Terminierung der anderen Seite wird durch entsprechende Widerstände auf dem letzten Board sichergestellt.

Das RENA System Interface übernimmt die Konfiguration<sup>8</sup> und die Kontrolle der einzelnen Boards, das zyklische Auslesen der Daten und deren Weitergabe an den Auswertecomputer. Auch in dem RENA System Interface werden alle Aufgaben von einem FPGA vom Typ Spartan XCS20 übernommen. Da weder das RENA Module Board noch das RENA System Interface über einen permanenten Konfigurationspeicher verfügen, muss zuerst das FPGA auf dem Interface vom Datenerfassungsprogramm über die PCI-Schnittstelle konfiguriert werden. Erst danach kann der binäre Datenstrom für die Konfiguration der FPGAs auf den installierten RENA Module Boards über das dann betriebsbereite Interface gleichzeitig an alle Boards übertragen werden.

Daten und Befehle werden über einen 4 Bit breiten bidirektionalen, synchronen Differentialbus (LVDS<sup>9</sup>) mit unidirektionalen Takt- und Steuersignalen übertragen. Die zusätzliche Leitung GLOBX wird bei der aktuellen Version des Boards nicht verwendet (Tabelle 2.1, Block *Communication group*).

Die differentielle Leitung IAOUT+/- überträgt das analoge Kontrollsignal aus einem ausgewählten Eingangskanal, das im Interface weiter verstärkt wird und zur Kontrolle und Abstimmung genutzt werden kann. Die Konfiguration des FPGAs geschieht über die vier Leitungen im Block *Initialization group*.

Über die Leitungen des Blocks *Power Group* versorgt das Interface die angeschlossenen *RENA Module Boards* mit den drei benötigten Versorgungsspannungen, Masse sowie den drei optionalen Hochspannungen für die Polarisation des Detektors.

<sup>&</sup>lt;sup>7</sup>Peripheral Component Interconnect, ein Bus-Standard für den Anschluß von Peripheriegeräten in Computersystemen.

<sup>&</sup>lt;sup>8</sup>Dieser Begriff wird in zwei verschiedenen Kontexten benutzt. Wird das RENA Module Board als eine eigenständige funktionale Einheit betrachtet, bedeutet Konfiguration das Einstellen der Betriebsparameter. Im Englischen könnte stattdessen das Wort Setup benutzt werden. Wird dagegen über das FPGA auf den Boards gesprochen, heißt Konfiguration das Übertragen des Bitstroms, welcher die Funktionalität des FPGAs bestimmt. Um Missverständisse zu vermeiden, wird in diesem Fall das FPGA ausdrücklich genannt.

<sup>&</sup>lt;sup>9</sup>Low Voltage Differential Signaling. Signalübertragungstechnik bei der das Signal als Spannungsdifferenz zwischen zwei parallelen Leitungen erfolgt. Dies verbessert wesentlich das Verhältnis zwischen Signal und Rauschen, da ein Störsignal die absolute Spannung beider Leitungen in gleichem Maße beeinflußt, nicht aber deren Differenz. Die Spannung kann auf diese Weise niedrig gehalten werden, was sich positiv auf die Schaltgeschwindigkeit auswirkt.

Tabelle 2.1: Belegung des Buskabels [NOV01]

| Signal name             | Type und direction                                              | Function                                                                                      |

|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| (Communication)         | tions group)                                                    |                                                                                               |

| CLK                     | LVDS to mod. boards                                             | 24.0000 MHz clock for all actions                                                             |

| BUSDAT[3:0]             | LVDS bidirectional                                              | data or command response from, and command to, the RENA boards                                |

| CMDVALID                | LVDS to mod. boards                                             | command valid on BUSDAT, going to the RENA boards                                             |

| GLOBX                   | LVDS to mod. boards                                             | global "X" line to the RENA boards - reserved (it could be used for pulser or SELALL trigger) |

| (Analog test            | output group)                                                   |                                                                                               |

| IAOUT+/-                | differential analog                                             | analog test output from RENA board                                                            |

| (Initialization         | /                                                               |                                                                                               |

| RESET                   | 5V CMOS w/ pullups                                              | reset all logic, but leave FPGA configured                                                    |

| PROGRAM                 | $5 \mathrm{V} \ \mathrm{CMOS} \ \mathrm{w/} \ \mathrm{pullups}$ | for FPGA configuration, see XCS20 data sheet                                                  |

| $\overline{	ext{INIT}}$ | $5 \mathrm{V} \ \mathrm{CMOS} \ \mathrm{w/} \ \mathrm{pullups}$ | for FPGA configuration, see XCS20 data sheet                                                  |

| DONE 5V CMOS            |                                                                 | for FPGA configuration, see XCS20 data sheet                                                  |

| (Power group            | o)                                                              |                                                                                               |

| GND                     |                                                                 | power and signal reference                                                                    |

| VSUPPLYA                | +6 to $+10$ V power                                             | source for VAA and VDD supply                                                                 |

| VSUPPLYB                | +10 to $+15$ V power                                            | power supply for voltage regulator circuit                                                    |

| VSUPPLYC                | +3.5 to $+10$ V power                                           | source for VRI supply                                                                         |

| VBIAS1                  | detector bias                                                   | configure by jumper as needed                                                                 |

| VBIAS2                  | detector bias                                                   | configure by jumper as needed                                                                 |

| VBIAS3                  | detector bias                                                   | configure by jumper as needed                                                                 |

Ein von NOVA erstelltes Windows-Programm, namens RENA Data Acquisition (DAQ), wird zur Konfiguration des Systems und zur Datenerfassung eingesetzt. Der Betrieb dieses Datenerfassungsprogramms sowie die Betriebsparameter für den Einsatz mit dem CdZnTe-Detektor sind ausführlich in [Suc04] beschrieben.

#### 2.1.1 Zeitstempel

Das System arbeitet mit einem Takt von 24.0 MHz, welcher von einem Quarz-Oszillator im *RENA System Interface* erzeugt wird und über das Buskabel an alle Boards verteilt wird. Aus diesem Takt wird im FPGA des Boards durch einen 1:8

Abbildung 2.5: Das RENA System Interface

Deutlich zu erkennen sind links hinten die LVDS-Treiber, in der Mitte das FPGA und rechts die Komponenten der Spannungsversorgung. Auf der Frontseite befinden sich, neben einer Reihe Kontroll-LEDs und der Reset-Taste, die Koaxialsteckplätze für die Bias-Spannung, der Analogausgang und die "X"-Leitung, die bei der hier eingesetzten Version der RENA Module Board nicht genutzt wird.

Frequenzteiler ein Sekundärtakt von 3.0 MHz erzeugt, der als Zeitbasis für einen 16 Bit breiten Zähler dient. Sollte der Detektor ein Ereignis auslösen, wird dieser Zählerstand als Zeitstempel dem Ereignisdatensatz, im folgenden Hit genannt, hinzugefügt. Der Zeitstempel hat somit eine Auflösung von  $1/3 \cdot 10^{-6}$  s und kann eine maximale Zeitspanne von  $2^{16} \cdot 1/3 \cdot 10^{-6} = 2.18$  ms erfassen, bevor der Zähler überläuft und wieder mit Null anfängt.  $^{10}$

Bei Messungen mit niedrigen Zählraten von ca. 500 Ereignissen pro Sekunde kann es vorkommen, dass der Zeitabstand zwischen zwei aufeinanderfolgenden Ereignissen so groß ist, dass zwei oder mehr Rollovers stattfinden und somit der reale Zeitabstand nicht rekonstruiert werden kann.

Bei langen Zeitabständen zwischen Ereignissen sammelt sich zudem Ladung aus Kriechströmen des Chips im Eingangsverstärker. Nach einem regulären Trigger verursacht das beim Auslesen des Kanals einen zu hohen Wert der gemessenen Spannung. Um dies zu vermeiden werden alle Kanäle regelmäßig zurückgesetzt.

<sup>&</sup>lt;sup>10</sup>Für dieses Verhalten wird in dieser Arbeit der gebräuchlichere englische Terminus Rollover benutzt

Wenn nach einer voreingestellten Zeitspanne nach einem Ereignis kein weiterer Trigger ausgelöst wird, sendet ein s.g. Watchdog Timer den Chips ein Forced Reset Signal und erzwingt dadurch die Leerung der Ladungsverstärker. Es wird dabei ein besonders markierter Hit erzeugt, dessen einzige signifikante Information der Zeitstempel ist (s. Abschn. 2.2.1).

Das Zeitintervall zwischen dem letzten regulären Trigger und dem Forced Reset, kann im Bereich von  $10-2560\,\mu s$  eingestellt werden. Ein kleiner Wert verbessert die Energiemessung, hat aber einen nachteiligen Einfluß auf die Totzeit. NOVA R&D empfiehlt einen Wert von  $560\,\mu s$ .

Wie im Abschnitt 5.2.1 gezeigt wird, ist es möglich, die *Forced-Reset-*Hits zu nutzen, um den Ereigniszeitpunkt auch bei sehr niedrigen Raten eindeutig zu bestimmen.

#### 2.2 Datenverkehr auf dem Bus

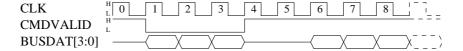

Das *RENA System Interface* sendet auf dem vier Bit breiten Datenbus Kontrollund Konfigurationsbefehle an die *RENA Module Boards* in Form von drei aufeinanderfolgenden Paketen (Nibble<sup>11</sup>).

#### Abbildung 2.6: Struktur des Datenpakets

Der Wechsel von High nach Low von CMDVALID signalisiert den RENA Module Boards den Beginn einer Befehlssequenz (Takt-Zyklen 1, 2 und 3). Unmittelbar nach der Rückkehr von CMDVALID zu logisch eins (H) beginnen die Boards den Befehl zu interpretieren. Auf Befehle des Typs Broadcast geben die Boards keine Antwort, Konfigurationsbefehle werden mit der Acknowledge Sequenz x5A in den Zyklen 6 und 7 quittiert, eventuell gefolgt von einem weiteren Nibble. Der Auslesebefehl kann nach dem Acknowledge mit bis zu 160 weiteren Datenpaketen beantwortet werden.

Die Kommunikation wird grundsätzlich vom Interface initiiert, indem die Leitung CMDVALID auf den Zustand  $Low^{12}$  gesetzt wird (s. Abb. 2.6) und die hexadezimale Adresse des angesprochenen Boards an den Datenbus für die Länge eines

$<sup>^{11}\</sup>mathrm{Eng.}$  kleines Stück, bezeichnet in der EDV die Hälfte eines Bytes, also eine Informationseinheit aus vier Bits. In den folgenden Abschnitten wird im Zusammenhang mit dem Datenverkehr auf dem RENA-Bus diese Bezeichnung benutzt. Angaben über ihren numerischen Inhalt werden meistens in der hexadezimalen Form mit vorangestellten x dargestellt, für die Binärdarstellung wird das Präfix b benutzt, z.B. x5A oder  $b0101\,1010$  für zwei Nibbles mit den dezimalen Werten 5 und 10. Um eine bessere Lesbarkeit zu erreichen, werden oft Gruppen von vier Ziffern durch ein Leerzeichen getrennt.

<sup>&</sup>lt;sup>12</sup>In der Digitaltechnik werden mit Low und High Spannungniveaus der Signalleitungen bezeichnet, die den logichen Zuständen 0 und 1 bzw. den Wahrheitswerten Falsch (False) und Wahr (True) entsprechen.

Takt-Zyklus angelegt wird. Es folgen zwei weitere Zyklen mit dem aus zwei Nibbles bestehenden eigentlichen Befehl. Nach dem Senden der drei Befehlsteile geht CMD-VALID wieder auf *High* und das Interface geht in den Empfangsmodus zurück und wartet auf die Antwort des angesprochenen Boards.

NOVA R&D hat einen Satz von Befehlen für die Boards definiert, die in zwei Klassen unterteilt werden. Einige dieser Befehle dienen der Konfiguration der Boards sowie ihrer Komponenten und der Einstellung der Messparameter, die anderen dienen der Kontrolle des Messbetriebs (siehe Tabelle 2.2).

In der ersten Spalte der Tabelle 2.2 sind die mnemonischen Symbole der Befehle aufgelistet. Die zweite Spalte enthält die hexadezimalen Werte der Befehlsfolge. Das erste Nibble, mit dem Stellvertreterzeichen <ID>, ist die Identifikationsnummer des adressierten Boards.

Bei den meisten Befehlen kann das letzte Nibble einen von zwei Werten annehmen (die Auswahlmöglichkeiten sind in eckige Klammern gesetzt, getrennt durch ein *Pipe-*Zeichen "|").

Mit Ausnahme des Auslesebefehls MB\_FIFO\_READ sind die Befehle für den Messbetrieb sogenannte *Broadcast*-Befehle, das heißt die Befehle sind nicht an ein spezielles Board adressiert. Sie sprechen alle Boards gleichzeitig an und erwarten daher keine Antwort. Das Stellvertreterzeichen ist in diesen Fällen <X>, da der tatsächlich übertragene Wert keine Bedeutung hat.

Die Antworten des Boards auf die Konfigurationsbefehle, in der dritte Spalte der Tabelle, beginnen immer mit der Acknowledge-Sequenz <ACK0> <ACK1> =x5A. Im Falle eines Schiebebefehls wird das niedrigwertigste Bit (LSB<sup>13</sup>) der Sequenz dem jeweiligen Register als LSB hineingeschoben. Das höchstwertigste Bit (MSB<sup>14</sup>) im Register wird herausgeschoben und als letztes Nibble der Antwort angehängt, so dass der alte Inhalt des Registers ausgelesen werden kann.

#### 2.2.1 Datenformat

Die komplexeste Antwort wird auf dem Auslesebefehl MB\_FIFO\_READ gegeben. Der *Acknowledge*-Sequenz folgt ein Nibble mit der Anzahl (zwischen 0 und 15) der mitgesendeten Hits.

Bis zu 32 Hits können von einem im FPGA des Boards realisierten FIFO<sup>15</sup>-Puffer zwischengespeichert und zum Auslesen bereitgestellt werden. Jeder Hit ist 40 Bit breit und wird als eine Sequenz von 10 Nibbles übertragen, angefangen mit dem

<sup>&</sup>lt;sup>13</sup>Least Significative Bit

<sup>&</sup>lt;sup>14</sup>Most Significative Bit

<sup>&</sup>lt;sup>15</sup>First In First Out

Tabelle 2.2: RENA-Befehle [NOV01]

| Symbol                         | Hex. Wert        | Antwort                                               | Funktion                                                                                                                          |

|--------------------------------|------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Betrieb<br>MB_FIFO_READ        | <id> 00</id>     | <ack0> <ack1> <cnt> <hits></hits></cnt></ack1></ack0> | Ruft Daten von <cnt> (0 bis 15) Hits auf</cnt>                                                                                    |

| MB_FIFO_CLEAR                  | < X > 10         | keine                                                 | Leert den Hit-Puffer                                                                                                              |

| MB_TIMER_CLEAR                 | <x> 11</x>       | keine                                                 | Zeitstempel auf Null setzten                                                                                                      |

| MB_WRITE_RUNFF                 | < X > 1[2 3]     | keine                                                 | Schaltet den Messbetrieb aus (2) oder ein (3)                                                                                     |

| Konfiguration<br>MB_RENA_SHIFT | <ID $>$ $C[0 1]$ | <ack0> <ack1> <out></out></ack1></ack0>               | Löscht (0) oder setzt (1) das MSB im<br>Schieberegister des RENA-Chips, der<br>alter Wert wird in <out> zurückge-<br/>geben</out> |

| MB_FEN_SHIFT                   | <ID $> C[2 3]$   | <ack0> <ack1> <out></out></ack1></ack0>               | Löscht (2) oder setzt (3) das MSB im Force-Enable Schieberegister                                                                 |

| MB_DAC_SHIFT                   | <ID> $A[0 1]$    | <ack0> <ack1> <out></out></ack1></ack0>               | Löscht (0) oder setzt (1) das MSB im DAC-Register und deaktiviert den DAC                                                         |

| MB_DAC_SHIFTEX                 | <ID> $A[2 3]$    | <ack0> <ack1> <out></out></ack1></ack0>               | Löscht (2) oder setzt (3) das MSB im<br>Register, schließt die Konfiguration des<br>DAC ab und reaktiviert ihn                    |

| MB_SHAD_SHIFT                  | <ID> $D[0 1]$    | <ack0> <ack1> <out></out></ack1></ack0>               | Löscht $(0)$ oder setzt $(1)$ das MSB im $shadow$ des CSR                                                                         |

| MB_SHAD_TO_CSR                 | <ID $>$ $D2$     | <ack0> <ack1></ack1></ack0>                           | Kopiert den Inhalt des $shadows$ in den CSR                                                                                       |

| MB_CSR_TO_SHAD                 | <ID $> D3$       | <ack0> <ack1></ack1></ack0>                           | Kopiert den Inhalt des CSR in den $shadow$                                                                                        |

MSB. Die dem *RENA*-Handbuch [NOV01] entnommene Tabelle 2.3 zeigt den Inhalt und das Format eines Hit-Datensatzes.

Je nach Auslesemodus werden entweder nur die Hits derjenigen Kanäle übertragen, welche einen Trigger ausgelöst haben, oder auch zusätzlich die Hits der dem auslösenden Kanal unmittelbar benachbarter Kanäle. Es ist alternativ auch möglich die Hits aller durch eine entsprechende Bitmaske des Chip-Registers eingeschalteten Kanäle zu übertragen.

Tabelle 2.3: Format des HIT-Datensatzes [NOV01]

| Bit Nr.    | Inhalt                                                                                                                                                                                          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIT[39]    | Forced-Reset Hit Wenn 1, wurde der Datensatz durch ein Forced-Reset ver-                                                                                                                        |

| HIT[38]    | ursacht. Nur der Zeitstempel ist signifikant.  FIFO Überlauf Wenn 1, war der FIFO vor der Annahme dieses Hits voll.  Einige Hits könnten verloren gegangen sein.                                |

| HIT[37]    | Abgeschnittenes Ereignis<br>Wenn 1, wurde die maximale Anzahl der Hits für dieses Ereignis überschritten.                                                                                       |

| HIT[36:23] | ADC-Daten, 14 Bits                                                                                                                                                                              |

| HIT[22:16] | Kanalnummer, 7 Bits<br>Bezieht sich nur auf den Kanal auf dem ausgelesenen Board.<br>Die eindeutige Identifizierung des Detektorkanals setzt sich<br>aus dieser Zahl und der Board-ID zusammen. |

| HIT[15:0]  | Zeitstempel, 16 Bits                                                                                                                                                                            |

Die maximale Anzahl der zu übertragenen Hits pro Ereignis kann auch auf einen Wert zwischen 1 und 15 Hits begrenzt werden. Sollte ein Ereignis mehr Kanäle ansprechen als in dieser Grenze angegeben sind, wird der letzte als *truncated* markiert (Bit 37 im Hit-Datensatz).

Alle von einem Ereignis generierten Hits werden am gleichen Wert des Zeitstempels erkannt.

### 2.3 Leistungsgrenzen

Wie bereits erwähnt, können mit einem Auslesebefehl bis zu 15 Hits von einem RENA Module Board zum Interface übertragen werden. Diese Operation kann bis

zu 168 Zyklen des 24.0 MHz Takts, also  $7\,\mu s$  dauern. Wenn eine kleine Wartezeit von 2 Taktzyklen  $(0,08\,\mu s)$  zwischen zwei aufeinanderfolgenden Lesevorgängen eingerechnet wird, ergibt sich eine maximale Datenrate von  $2,1\cdot 10^6\,\mathrm{Hit/s}$ .

Da jeder Hit eine Länge von 10 Nibbles bzw. 5 Bytes besitzt, sollte das System aus RENA System Interface und DIO-96-Schnittstelle bei Auslastung der angesteuerten RENA Module Boards respektive angeschlossenen Detektoren eine Übertragungsrate von  $10,1\,\mathrm{MByte/s}$  bewältigen.

Messungen sowohl am IAAT als auch am UCSD/CASS haben einen maximalen Durchsatz dieses Systems von etwa  $50.000\,\mathrm{Hit/s}$  gezeigt, der somit weit unter den Möglichkeiten der RENA Module Boards liegt.

Eine sorgfältige Analyse des Systems hat folgende Wege aufgezeigt, um eine Steigerung des Datendurchsatzes zu erreichen.

Als offensichtliches Nadelöhr wurde die eingesetzte Datenerfassungskarte für den PCI-Bus identifiziert, die laut Handbuch [Nat96, App. A] nur eine Transferrate von maximal 780 KByte/s leisten kann.

Aus der Analyse der VHDL-Quellen<sup>16</sup> des *RENA System Interface* ergibt sich, das für Daten nur ein Puffer von 13 Byte verwendet wurde, eventuell wegen der sehr begrenzten Ressourcen des *Spartan XCS20* FPGAs. Dies schränkt die Transferrate zusätzlich ein, z.B. für den Fall dass der Datenerfassungscomputer mit anderen Aufgaben beschäftigt ist und der Datenstrom kurzfristig unterbrochen werden muss.

Um sowohl die Leistungfähigkeit zu erweitern, als auch aus dem Wunsch nach höherer Flexibilität und der Möglichkeit Treiber und Software auch für das Linux Betriebssystem realisieren zu können, ist das Projekt entstanden, das *RENA System Interface* neu zu entwickeln.

<sup>&</sup>lt;sup>16</sup>VHSIC Hardware Description Language. VHSIC steht für *Very High Speed Integrated Circuit*. Ein hervorragendes Werk über VHDL findet sich in [Ash02], ein einfaches und leicht verständliches Einstieg ist [ST04]. Siehe auch Anhang A.1

## Kapitel 3

## **RENA Control Interface**

Das RENA Control Interface (RCI) ist eine Weiterentwicklung des RENA System Interface von NOVA R&D. Es besteht aus einer speziell entwickelten Versorgungsplatine und der FPGA-Hardware die in Kapitel 4 besprochen wird.

Das Ziel dieser Arbeit war nicht, ein komplett neues Gerät zu konstruieren, sondern vor allem eine leistungsfähigere Schnittstelle für den Datenaustausch mit dem PC zu entwickeln. Die Anforderungen, welche die Kompatibilität zum RENA System Interface stellt, können wie folgt zusammengefasst werden:

- $\bullet$ Bereitstellung der drei Versorgungsspannungen von 3,3 V und 5,8 V bei 1,5 A und 11,0 V bei 0,5 A, ausreichend für die Versorgung von 8 RENA Module Boards

- Versorgung der Boards mit dem Taktsignal von 24 MHz

- Differentielle Buskommunikation (LVDS)

- $\bullet$  Verstärker für das analoge Testsignal mit Bandbreite von 160 MHz und Verstärkung von 95 dB

- Konfiguration der FPGAs auf den RENA-Boards

- Direkte Weiterleitung der RENA-Befehle vom PC an die Boards

- Empfang der Antworten der Boards auf *RENA*-Befehle und Bereitstellung zum Auslesen durch den PC

- Möglichkeit zur Adressierung von bis zu 16 Boards

- Kontinuierliches, zyklisches Auslesen aller am Bus angeschlossenen Boards

Die neue Schnittstelle soll die Aufgaben des RENA System Interface ohne Abstriche erfüllen können aber vor allem dazu fähig sein, seine maximale Datenrate von ca. 50.000 Hit/s wesentlich zu übertreffen. Idealerweise sollte die rechnerische maximale Rate der RENA Module Boards von  $2, 1 \cdot 10^6$  Hit/s erreicht werden.

Darüberhinaus soll, speziell für Zeitreihenmessungen, auch eine Mögligkeit gegeben werden, die Uneindeutigkeit der Zeitinformation bei niedrigen Zählraten, über die im Abschnitt 2.1.1 berichtet wurde, zu beheben ohne die Kommunikation mit der

Übertragung der ansonsten unnötigen Forced-Reset-Hits zu belasten. Ausserdem sollen die Zeitstempelzähler mit einem genaue Zeitgeber, z.B. einem GPS- oder Funkuhrempfänger, jede Sekunde synchronisiert werden können.

Weiter sollen Verbesserungen und zusätziche Leistungsmerkmale realisiert werden, um eine höhere Flexibilität bei dem Einsatz mit moderne PC-Systeme im Labor zu erlauben. Unter Anderem soll ein größerer Abstand zwischen PC und Messelektronik als der mit dem RENA System Interface derzeit mögliche Abstand von einem Meter erlaubt sein. Dies ist sowohl wegen der besseren Möglichkeit zur Abschirmung der Detektoren vor dem störenden Einfluß eines PCs und seines Bildschirms erwünscht, als auch um einen besseren Schutz des Bedienpersonals vor der zu messende Röntgenstrahlung zu gewährleisten.

Als Kommunikationsschnittstelle hat sich der *Universal Serial Bus* (USB<sup>1</sup>) als eine gute Alternative zur *DIO-96* Schnittstelle erwiesen, da er alle gestellten Anforderungen in Bezug auf Leistung, Verfügbarkeit und Zuverlässigkeit erfüllt. Durch seine hohe Verbreitung findet man geeignete und preiswerte Komponenten auf dem Markt. Dank der verfügbaren Dokumentation ist es möglich, Software für den Einsatz unter Windows oder Linux mit vertretbarem Aufwand zu entwickeln.

Ein leistungsfähiges FPGA sollte alle Verwaltungsaufgaben und die Kommunikation sowohl mit den RENA Module Boards als auch mit dem USB-Chip übernehmen. Gleichzeitig sollte das RCI, aus der Sicht der RENA Module Boards, soweit möglich zum alten Interface kompatibel gestaltet werden. Vor allem die elektrischen Eigenschaften des Datenbuses und die Qualität und Leistung der Stromversorgung sollten dem Original möglichst ähnlich sein. Es war daher pragmatisch, aus den von NOVA R&D mit dem System gelieferten Schaltplänen die Teile, die nicht an der Kommunikation mit dem Auswertecomputer beteiligt sind, zu übernehmen.

Der Schwerpunkt dieser Arbeit besteht in der Entwicklung eines VHDL-Designs für die Konfiguration des FPGAs, auf das in den Kapiteln 4 und 5 eingegangen wird. Die folgenden Abschnitte beschreiben zunächst nur die Hardware, also die Versorgungsplatine des RCIs und die daran angeschlossenen Zusatzmodule.

#### 3.1 "Swatter"

Das für diese Entwicklung gewählte FPGA ist ein XILINX Virtex-II XC2V1000, es bietet für diesen Zweck ausreichend große Ressourcen und befindet sich, zusammen mit einem USB-Chip vom Typ Cypress AN2131 auf dem Entwicklungsmodul Swatter der Firma  $DD\mathcal{E}T$ .

<sup>&</sup>lt;sup>1</sup>Anhang B stellt eine kurze Einführung in die USB Technologie dar, darin werden hauptsächlich die Struktur und die Eigenschaften der Hardware und das *Low-Level-*Kommunikationsprotokoll beschrieben.

Abbildung 3.1: Der Swatter von DD&T

Das FPGA, leicht rechts von der Mitte, ist ein Virtex-II XC2V1000. In der unteren rechten Ecke befindet sich das USB-Chip Cypress AN2131 und unten links die Stromversorgung. An der obere Kante erkennt man die Kontakte des an der Unterseite angebrachten VG96-Steckers für den Anschluß an den Prototyp.

Ein solches Modul eignet sich speziell für die Entwicklung von Prototypen, da es nur eine oder wenige Kernkomponenten beinhaltet, deren Einbau in einem Prototyp zu teuer und zu aufwendig wären.

Das FPGA auf dem Swatter hat ein Gehäuse in FG256-Ausführung. Seine 256 Kontakte sind auf der Unterseite in einer Matrix von 16x16 kleinen Lötkugeln im Abstand von 1 mm angeordnet (Ball Grid Array, BGA). Da Komponenten dieses Typs nur in spezialisierten Werkstätten auf die Platinen gelötet werden können, erhöht dies zusätzlich die Kosten und den Zeitaufwand für die Realisierung eines Prototyps. Daher werden solche Komponenten auf einem separaten Modul zur Verfügung gestellt, das einfach auf die verschiedenen Entwicklungsstufen der neuen Platine eingesteckt werden kann.

Die Konfiguration des FPGAs kann beim Swatter nur über die JTAG-Schnittstelle<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> Joint Test Action Group ist der Name eine Arbeitsgruppe, die ein Verfahren zur Fehlersuche (Debugging) bei Hardware im Jahre 1985 entwickelt hat. Das Kürzel JTAG ist die Bezeichnung für das Verfahren selbst und für die damit in IEEE 1149.1 (Norm des amerikanisches Institute of Electrical and Electronics Engineers) standardisierte serielle Schnittstelle und wird inzwischen vermehrt zur Konfiguration von FPGAs bzw. CPLDs (Complex Programmable Logic Device, s. Anh. A) und zur Programmierung von Mikroprozessoren verwendet.

erfolgen, da er über keinen nichtflüchtigen Speicher für die Konfigurationsdaten verfügt. Um einen Stand-Alone Betrieb zu ermöglichen, wurde am IAAT ein zusätzliches Speichermodul (s. Abb. 6.1) entwickelt, das nach geringfügigen Veränderungen am Swatter (einige Leitungen mußten zusätzlich verbunden werden) huckepack auf das Board gesteckt werden kann. Die JTAG-Schnittstelle kann dann dazu benutzt werden, die Konfiguration wahlweise direkt in das FPGA oder in das EEPROM zu laden.

Der USB-Chip des Swatters entspricht der USB-Spezifikation 1.1, unterstützt also den Full-Speed-Betrieb (siehe Anhang B) mit einer nominalen Tranferleistung von 12 MBit/s.

Der Swatter wurde eingesetzt, obwohl es sich dabei um einen Prototyp handelt, und die maximale Bandbreite des USB 1.1 Chip von 9,7 MBit/s die Leistung des RENA System Interface nur um den Faktor 1,5 übersteigt.

Die in Aussicht gestellte nächste Version des Swatters soll ein FPGA gleichen Typs besitzen sowie die gleiche Pinbelegung aufweisen und zusätzlich über ein serielles EEPROM und einen USB 2.0 Chip verfügen.

Um nicht auf die Fertigstellung des neuen Swatters warten zu müssen und trotzdem schon mit USB 2.0 arbeiten zu können, wurde provisorisch ein Stück Lochrasterplatine am RCI angebracht und an freie Pins der VG96-Buchse gelötet (s. Abb. 3.4). Dies erlaubte den Einsatz eines separaten USB-2-Moduls.

#### 3.2 Eingesetztes USB-Modul

Das USB High Speed Interface Modul 2.5 der Firma BrainTechnology in Frankfurt/Main basiert auf dem USB-Chip Cypress CY7C68013.

Dieses Modul stellt drei 8 Bit breite I/O-Ports sowie einige Kontrollleitungen zur Verfügung, die je nach Betriebsmodus verschiedene Funktionen erfüllen.

Die Firmware kann in einem 8 KByte großen seriellen EEPROM gespeichert werden, und wird in diesem Fall von einer getrennt zu erwerbenden  $\rm DLL^3$  auf den Chip übertragen.

Die DLL stellt zugleich eine Programmierschnittstelle (Application Programming Interface, API) mit einer großen Anzahl von Funktionen bereit, mit der, beim Programmieren eigener Windows-Anwendungen, auf sehr einfache Weise auf die Funktionalität des Moduls zugegriffen werden kann.

<sup>&</sup>lt;sup>3</sup>Dynamic-Link Library, eine Bibliothek für das Betriebssystem Microsoft Windows. Eine DLL ist ein Programm das keine eigene Benutzeroberfläche bereitstellt. Die in ihr implementierten Funktionen werden dynamisch, d.h. nach Bedarf vom Betriebssystem in den Speicher geladen und dem aufrufenden Programm zur Verfügung gestellt. Wenn diese Funktionen nicht mehr benötigt werden, entfernt sie das Betriebssystem wieder aus dem Speicher.

Der Entwickler der DLL und der Firmware hat auch über GPIF 10 verschiedene Betriebsmodi für parallele Datenübetragungen auf 8 und 16 Bit implementiert, sowie die Möglichkeit alle 24 Leitungen der 3 I/O-Ports voneinander unabhängig zu lesen oder zu setzen.

Abbildung 3.2: USB-Modul von BrainTechnology

#### 3.3 RCI-Versorgungsplatine

Der Haupteil des RCI wird als Hardware innerhalb des FPGAs erzeugt. Da der Swatter alle für den Betrieb des FPGAs notwendigen Komponenten beinhaltet und genügend I/O-Ports über den VG96-Stecker zur Verfügung stellt, war es ausreichend eine Platine zu entwerfen, die über einen VG96-Anschluß den Swatter an den LVDS-Treiber anschließt und die Stromversorgunskomponenten unterbringt.

Mit Hilfe des Softwarepakets Altium Protel2004 wurden sowohl der Schaltplan (siehe Abbildung 3.3) entworfen als auch die doppelseitige Platine im Format  $10 \times 16 \,\mathrm{cm}^2$  (Euro-Standand) entflochten. Es wurden dabei Bauteile in klassischer und in SMD<sup>4</sup>-Technologie eingesetzt.

#### 3.3.1 Stromversorgung

Eine der drei für den Betrieb der *RENA Module Boards* notwendigen Versorgungsspannungen (VSUPPLYB = +11,0 V) und die Hauptversorgung (Vcc = +5,0 V)

<sup>&</sup>lt;sup>4</sup>Surface Mounted Device

Abbildung 3.3: RENA Control Interface, Schaltplan

aller Komponenten des RCIs und des Swatters, werden von dem rauscharmen Spannungsreglern U1 und U2, beide vom Typ MICREL MIC5209, erzeugt.

Da es nicht möglich war, die Originalteile LT1763 von  $Linear\ Technology$  auf dem europäischen Markt zu finden, war es in diesem Fall notwendig, sie durch den Typ MIC5209 zu ersetzen.

Beide Typen haben sehr ähnliche Leistungsmerkmale, benötigen aber leicht unterschiedliche Anordnungen der Steuerkomponenten, so dass es hier Abweichungen von der Originalschaltung gibt.

Die restlichen zwei Versorgungsspannungen der Boards (VSUPPLYA =  $+5,8\,\mathrm{V}$  und VSUPPLYC =  $+3,3\,\mathrm{V}$ ) werden von den integrierten Schaltnetzteilen U3 und U4 vom Typ Linear Technology LT1375 erzeugt. Zur Minimierung des Rauschens werden ihre internen Oszillatoren, durch ein Referenzsignal von 600 KHz mit dem Takt des FPGAs synchronisiert (SWSYNC). Dieses Signal wird aus dem Systemtakt von 48 MHz durch einen 1:80 Frequenzteiler im FPGA erzeugt und, entsprechend der Herstellerspezifikationen, erst dann an die Schaltnetzteile geliefert, nachdem eine positive Spannung an der Leitung SWSYNCEN an die Schaltnetzteile gelegt wurde.

Die Schaltnetzteile sind für eine maximale Last von 1,5 A und die Spannungsregler für einen Strom von 0,5 A ausgelegt, was laut der Dokumentation von NOVA R&D [NOV01] ausreicht, bis zu 8 Boards am Bus zu betreiben.

Beide Typen von Stromversorgungskomponenten können abgeschaltet werden, wenn die Spannung an ihren Freigabepins die jeweiligen Referenzwerte unterschreitet. Durch entsprechende Spannungsteiler-Netzwerke an diesen Pins kann die Abschaltung des gesamten Systems veranlasst werden, falls die Spannung an der Versorgungsbuchse P1 unterhalb den für den Betrieb erforderlichen Wert von 13 V liegen sollte.

Die maximal erlaubte Spannung an P1 liegt bei 19 V. Es wurde keine Schutzvorrichtung gegen die Überschreitung dieses Pegels eingebaut.

#### 3.3.2 LVDS-Bustreiber

Die bidirektionale Konvertierung der CMOS-Signale des FPGAs, die an der VG96-Buchse JP3 anliegen, in das differentielle Format des *RENA*-Datenbus (siehe Abschnitt 2.1 bzw. Tabelle 2.1) wird von den vier LVDS-Einzeltransceivern U5 bis U8 vom Typ *National Semiconductor DS92LV010A* übernommen.

Die Umschaltung von Empfang- zum Sendebetrieb erfolgt durch Anlegen einer positiven Spannung am  $Driver\ Enable\ (DE)$  Eingang über die Signalleitung BUSOE des FPGAs. Zwischen dem negativen und dem positiven Anschluß jedes Transceivers ist ein Widerstand von  $133\,\Omega$  für die Terminierung des Busses angebracht.

Die IC U9 ist ein vierfacher LVDS-Treiber vom Typ DS90C031TM von National Semiconductor für die Konvertierung der drei unidirektionalen Steuersignale.

#### 3.3.3 Weitere Anschlüsse

Das differentielle Analogsignal aus der Testleitung der Boards wird durch den Operationsverstärker U10A an der *LEMO*-Koaxialbuchse J1 zur Verfügung gestellt. Bei U10A handelt es sich um einen Hochleistungsverstärker mit einer Bandbreite von 160 MHz und einer maximalen Verstärkung von 95 dB.

Da der in dem RENA System Interface eingebaute Verstärker AD8041 von Analog Devices nicht lieferbar war, wurde hier eine Hälfte des doppelt ausgeführten Verstärkers AD8042 eingesetzt, der die gleichen Eigenschaften wie das Original aufweist.

Über die Koaxialbuchse J2 kann eine Spannung von bis zu 500 V für den Detektor-Bias angelegt werden. Nach einem Entstörfilter wird sie über den Bus-Stecker JP4 direkt an die RENA Module Boards geleitet.

Die Koaxialbuchse J3 dient der Einspeisung eines 1 Hz Signals für die Synchronisation der Zähler, welche die Zeitstempel erzeugen.

Neben der VG96-Buchse für den Swatter befinden sich auf der Platine zwei 40-polige Messerleisten für Flachbandkabel. Diese sind für den Anschluß eines *Logic Analyzers* vorgesehen und sind direkt mit der VG96-Buchse verbunden.

Das RENA-Buskabel wird an der SMD-Messerleiste JP2 angeschlossen.

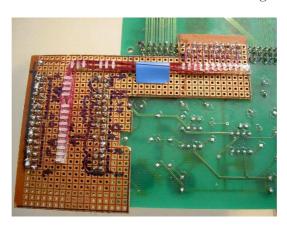

Abbildung 3.4: Zwischenlösung für USB

Das Bild zeigt die Unterseite der Lochrasterplatine, die den Swatter mit dem separaten USB-2-Modul verbindet. Die Pins der vier Pinleisten, auf das Modul aufgesteckt wird, wurden durch Einzeldrahtverbindungen an freien Pin des VG96 angeschlossen.

Abbildung 3.5: Vollständig bestückte Hauptplatine

Links von der VG96-Buchse sind die zwei Schaltnetzteile U3 und U4 untergebracht, da sie Elektrolytkondensatoren benötigen, die unter dem Swatter keinen Platz haben. Alle weiteren Komponenten sind sehr kompakt zwischen den blauen Messerleisten angeordnet. Die Widerstände R2, R7, R10 und R12 wurden durch Prezisionstrimmer ersetzt, um die erzeugten Spannungen fein einstellen zu können. Die braune Platine unten links wurde nachträglich eingesetzt um das USB-Modul anzuschließen (s. Abschn. 3.2).

# Kapitel 4

# VHDL-Design - Aufbau

Das Modell oder Design für die Konfiguration des FPGAs wurde mit Hilfe der  $Hardware\text{-}Beschreibungssprache\ VHDL^1$  entworfen.

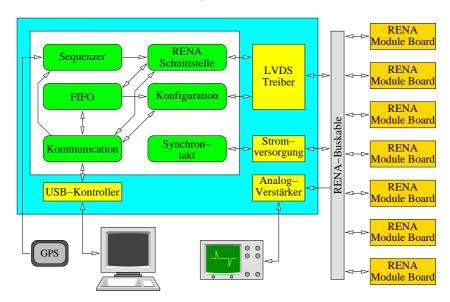

Das Blockdiagramm des RCIs ist in Abbildung 4.1 dargestellt. Das RCI selbst wird durch das blaue Rechteck, die Hardwarekomponenten durch gelbe Blöcke symbolisiert. Das FPGA entspricht der weißen Fläche, darin befinden sich die sechs logischen Komponenten, aus denen das RCI-Design besteht. Sie sind durch Pfeile, die den Datenfluss zwischen ihnen verdeutlichen, verbunden.

Abbildung 4.1: Blockdiagramm des RCIs

Auf der rechten Seite ist das RCI an das Bus-Kabel angeschlossen zusammen mit einigen  $RENA\ Module\ Boards$ , unten ist ein Oszilloskop mit dem analogen Überwachungsausgang und der Datenerfassungs-PC mit dem USB-Kontroller verbunden.

$<sup>^1{\</sup>rm Siehe}$  Fußnote 16 auf Seite 18 sowie Anhang A.1

Das graue Kästchen unten links symbolisiert einen GPS-Empfänger, der den Sekundentakt für die Synchronisation der Zeitstempelzähler liefert.

Die Aufgaben des RCI werden von vier Modulen, die im Kapitel 5 näher erläutert werden, übernommen:

- Die RENA-Schnittstelle bereitet die RENA-Befehle, die entweder vom Sequenzer oder direkt von der Auswertungssoftware auf den PC über die Kommunikationsschnittstelle kommen, für die RENA Module Boards vor und speichert ihre Antwortdaten in dem FIFO-Puffer.

- Der Auslesesequenzer erzeugt die Befehlsfolge für das zyklische Auslesen aller installierten *RENA Module Boards* und die Synchronisation der Zeitstempelzähler.

- Das Konfigurationsmodul übermittelt den Konfigurationsbitstrom an die FPGAs der Boards und überwacht ihren Status.

- Die Kommunikationsschnittstelle sorgt für die Übertragung von Daten und Befehlen zwischen dem USB-Kontroller und den RCI-Modulen.

Beim FIFO-Puffer handelt es sich um eine von XILINX vordefinierte Standardkomponente (Core), die vom Benutzer auf die gewünschte Größe konfiguriert wird. Der Speicherpuffer hat eine Wortbreite entsprechend der Breite des USB-Datenbus von 16 Bits und, in diesem Stadium der Entwicklung, eine Tiefe von 256 Worten.

Das Symbol mit der Beschriftung Synchrontakt im Blockdiagramm (Abb. 4.1) stellt kein eigenständiges Modul dar. Es handelt sich um einen einfachen Frequenzteiler mit Freigabeport, wie in Abschnitt 3.3.1 erläutert, der als eigenständiger Prozess direkt innerhalb des Top-Level-Moduls (s. Abschn. 5.1) implementiert ist.

## 4.1 Funktionsprinzip

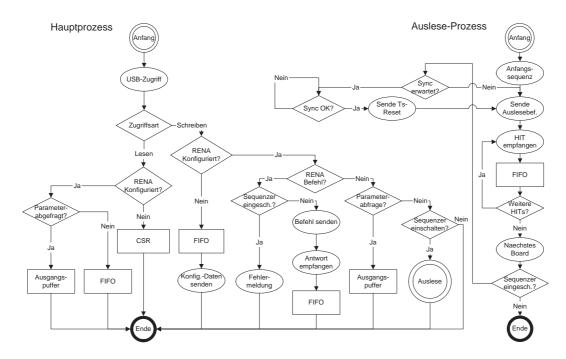

Das Funktionsprinzip des RCIs wird anhand eines vereinfachten Flussdiagramms, das in Abbildung 4.2 dargestellt ist, deutlich gemacht.

Bei der Inbetriebnahme lädt das FPGA des RCIs seine Konfiguration aus dem EEPROM (s. Abschn. 3.1 und Abb. 6.1) und ist nach wenigen Sekunden betriebsbereit. Da die RENA Module Boards kein EEPROM besitzen, werden ihre FPGAs mit Hilfe des RCIs konfiguriert. Die FPGAs der Boards signalisieren diesen Zustand durch ein Low auf einer spezielle Leitung des Buskabels. Wird dieser Zustand erkannt, steht dem Benutzer bzw. der Auslesesoftware nur ein begrenzter Funktionsumfang zur Verfügung.

Bei noch nicht betriebsbereiten RENA Module Boards kann nur der Inhalt des  $CSRs^2$  ausgelesen werden, Schreibzugriffe dürfen in dieser Phase nur der Konfigu-

<sup>&</sup>lt;sup>2</sup>Das Control and Status Register enthält einige Betriebsparameter und Statusinformationen

Abbildung 4.2: Flussdiagramm der RCI-Befehle

Der Hauptprozess wird bei der Inbetriebnahme gestartet und reagiert auf Zugriffe des USB-Kontrollers. Der Auslese-Prozess läuft unabhängig vom Hauptprozess und wird von einem entsprechenden Befehl gestartet.

ration der FPGAs der Boards dienen. Alle ankommenden Daten werden in den FIFO-Puffer geschoben und sofort an die Boards weitergeleitet.

Sind die FPGAs der Boards erfolgreich konfiguriert, werden Schreibzugriffe des USB-Kontrollers als Befehle interpretiert. Alle bisher definierten 16 Bit breiten Befehle sind in Tabelle 4.1 aufgelistet.

Bei Lesezugriffen wird in der Regel der Inhalt des FIFO-Puffers oder, bei leerem FIFO, ein Null-Paket (x0000) übertragen. Zwei der RCI-Befehle (die "RCI\_GET"-Befehle) fordern Information über den momentanen Zustand des RCIs an. Da diese Information nur sehr kurzfristig von Bedeutung ist, werden die angeforderten Daten in einem Ausgangspuffer zwischengespeichert und bei dem diesen Befehlen unmittelbar folgenden Lesezugriff ausgegeben. Der Ausgangspuffer wird danach gelöscht und weitere Lesezugriffe liefern wieder den FIFO-Inhalt. Werden mehrere RCI\_GET-Befehle hintereinander gesendet, bezieht sich der Inhalt des Ausgangspuffers nur auf den letzten Befehl. Wird anstatt des Lesezugriffs nach einem RCI\_GET-Befehl ein anderer Befehl gesendet, dann wird der Ausgangspuffer sofort gelöscht.

Die Befehle RCI\_SEQ\_START, RCI\_SEQ\_START\_FR und RCI\_SEQ\_STOP steuern den Betrieb des Auslesesequenzers. Dieser Prozess (rechts im Flussdiagramm,

Symbol Wert **Funktion** RCI\_NULL x0000Nullbebefehl, hat keine Funktion Startet die Auslesesequenz, <ID> ist die höchste RCI\_SEQ\_START x001 < ID >ID-Nummer der installierten Boards RCI\_SEQ\_START\_FR x002 < ID >Wie oben, überträgt auch Forced-Reset-Hits RCI\_SEQ\_STOP x003 < X >Stoppt die Auslesesequenz RCI\_GET\_CSR Setzt den Inhalt des CSRs in den Ausgangspuffer x004 < X >RCI\_GET\_DCOUNT x005 < X >Setzt die Anzahl der FIFO-Einträge in den Ausgangspuffer Leert den FIFO-Puffer RCI\_FIFO\_CLEAR x006 < X >RCI\_RENA\_CONFIG xE000Reinitialisiert die FPGAs der Boards RCI\_RENA\_RESET xE001Reset-Signal für die Boards RCI\_RENA\_CMD xF < CMD >Sendet den 12 Bit breiten RENA-Befehl <CMD>

Tabelle 4.1: RCI-Befehle

Abb. 4.2) läuft parallel zum Hauptprozess und davon völlig unabhängig. In einer Dauerschleife werden nacheinander alle installierten RENA Module Boards ausgelesen, die empfangene Hits-Datensätze ergänzt und formatiert und in den FIFO-Puffer gespeichert. Die Schleife wird 7,2  $\mu$ s bevor ein neuer Puls für die Synchronisation der Zeitstempelzähler erwartet wird angehalten. Diese Zeitspanne reicht aus, den längstmöglichen Auslesevorgang zu beenden, bevor bei Ankunft des Pulses der RENA-Befehl für die Löschung der Zeitstempelzähler abgeschickt und die Schleife wieder gestartet wird.

Durch den Befehl RCI\_RENA\_CONFIG wird die Löschung der FPGA-Konfiguration aller RENA Module Boards erzwungen und eine erneute Konfiguration notwendig gemacht. Dagegen setzt RCI\_RENA\_RESET die Boards nur in den Ausgangszustand zurück, ohne die Konfiguration der FPGAs zu löschen.

Beim Befehl RCI\_RENA\_CMD handelt es sich nur um einen 4 Bit breiten Header, der einem RENA-Befehl vorgestellt wird. Die RENA-Befehle können so erkannt und sofort unverändert an die Boards weitergeleitet werden. Die Antworten der Boards auf diese Befehle werden auch formatiert und im FIFO-Puffer gespeichert. Solange der Sequenzer in Betrieb ist, werden diese Befehle vom RCI zurückgewiesen.

Der Befehl RCI\_FIFO\_CLEAR leert nur den FIFO-Puffer des RCIs. RCI\_NULL hat keine besondere Funktion, das RCI quittiert den Befehl an den USB-Kontroller und ignoriert ihn. Er kann zum Testen der USB-Verbindung genutzt werden.

Der Adressbereich von x0070 bis xDFFF ist frei und kann für zukünftige Zwecke genutzt werden.

#### 4.2 Datenformate

Bedingt durch die Breite des Datenbus von 16 Bits, werden Daten in ebenso breiten Paketen vom RCI geliefert.

Entsprechend ihrem Inhalt, werden die Pakete mit einem 3 oder 4 Bit breiten Datenkopf (*Header*) an ihrem Anfang (der MSB) versehen, um sie unabhängig vom Zeitpunkt ihrer Abholung durch den Auswertungscomputer unterscheiden und einordnen zu können.

Tabelle 4.2 zeigt die bis zu diesem Zeitpunkt definierten Header und den Inhalt der Pakete.

| Symbol         | Wert                          | Bedeutung                                      |

|----------------|-------------------------------|------------------------------------------------|

| HDR_NULL       | x0000                         | Null-Paket                                     |

| Adressbereich  | x0001 - x2FFF                 | Nicht definiert, frei für künftige Anwendungen |

| HDR_CSR        | b0011 < CSR >                 | Inhalt des CSRs (12 Bits)                      |

| HDR_FIFO_COUNT | b0100 < CNT >                 | Anzahl der FIFO-Einträge<br>(Ganzzahl, 12 Bit) |

| HDR_RENA_FAIL  | b0101 < CMD >                 | Unbeantworteter $RENA$ -Befehl                 |

| HDR_RENA_CMD   | $b011[0 1]{<}\mathrm{CMD}{>}$ | Antwort und $RENA$ -Befehl                     |

| HDR_HIT0       | $b100{<}\mathrm{HIT}0{>}$     | Erster Teil eines Hits (13 Bits)               |

| HDR_HIT1       | b101 < HIT1 >                 | Zweiter Teil eines Hits (13 Bits)              |

| HDR_HIT2       | $b110 {<} \mathrm{HIT2} {>}$  | Dritter Teil eines Hits (13 Bits)              |

| HDR_HIT3       | b111 < HIT3 >                 | Vierter Teil eines Hits (13 Bits)              |

Tabelle 4.2: Header und Inhalt der Datenpakete

Bei HDR\_NULL, das wie der freie Adressbereich in der Tabelle in hexadezimaler Form dargestellt ist, handelt sich genaugenommen nicht um einen Header, sondern um das gesamte Null-Paket. Der Inhalt des 12 Bit breiten Control und Status Registers und des  $4\times13$  Bit breiten Hit-Datensatzes ist in Tabelle 4.3 angegeben.

${\bf Tabelle~4.3:}$ Formate der CSR- und Hit-Datensätze

| Bit   | Bedeutung                                 |  |

|-------|-------------------------------------------|--|

|       | Control und Status Register               |  |

| 11-9  | Unbenutzt, frei für künftige Anwendungen  |  |

| 8     | RENA-FPGAs sind konfiguriert              |  |

| 7     | RCI-FIFO ist voll                         |  |

| 6     | RCI-FIFO ist leer                         |  |

| 5     | Speichern der Forced-Reset-Hits ist aktiv |  |

| 4     | Sequenzer in Betrieb                      |  |

| 3-0   | Höchste ID der installierten Boards       |  |

| Hit   |                                           |  |

| 51    | RCI-FIFO war voll vor diesem Hit          |  |

| 50    | Zeitstempel-Warnflagge                    |  |

| 49    | Forced-Reset-Hit                          |  |

| 48    | $RENA	ext{-}FIFO$ war voll vor diesem Hit |  |

| 47    | $Truncated	ext{-}Event	ext{-}Error$       |  |

| 46-41 | Zeitstempel-Erweiterung                   |  |

| 40-25 | RENA-Zeitstempel                          |  |

| 24-21 | Board-ID                                  |  |

| 20-14 | Kanalnummer                               |  |

| 13-0  | ADC-Daten                                 |  |

# Kapitel 5

# VHDL-Design - Detaillierte Darstellung

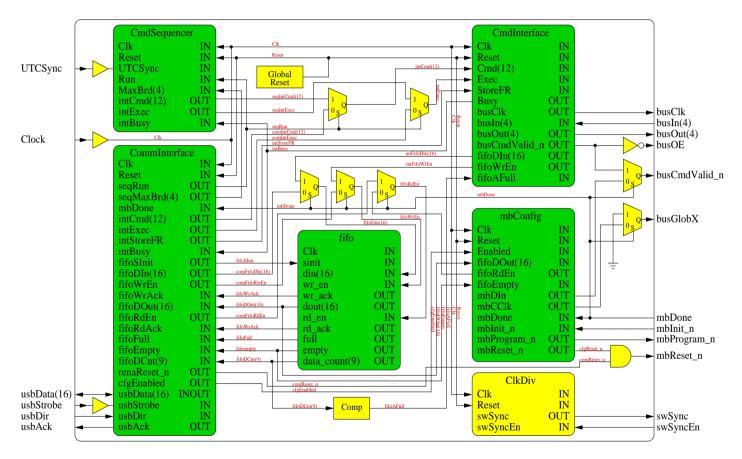

### 5.1 Top-Level-Modul

Das Top-Level-Modul eines VHDL-Designs bildet den Rahmen, in dem die einzelnen Module instanziert und miteinander verbunden werden. Abbildung 5.1 zeigt detailliert seine Struktur. Das Top-Level wird durch die schwarze Umrandung dargestellt, rechts und links außerhalb dieser Umrandung befinden sich die Ports seiner Schnittstelle, die zugleich die Schnittstelle des RCIs bilden.

Alle Module sind durch grüne Rechtecke dargestellt. Ihre Schnittstellen sind genau aufgeführt, mit Angabe über die Breite und die Richtung der Ports. Die Pfeile zeigen die Richtung und die Art der Verbindung der Signale.

Die gelben Symbole stehen für logische Bausteine, die durch bedingte Signalzuweisungen oder als Prozess, wie den oben erwähnten Frequenzteiler (ClkDiv), in dem Architecture-Teil des Moduls definiert werden. Die Eingangspuffer für die Leitungen UTCSync, Clock und usbStrobe sind feste Bestandteile der FPGA-Architektur und sollen in dem Design für Taktsignale oder andere periodische Signalen instanziert werden. Sie sorgen für die korrekte Benutzung der Takt-Verteilerbäume und für die Entzerrung des Signals. Professionelle Synthesewerkzeuge können allerdings in der Optimierungsphase solche Signale erkennen und ihnen die passenden Eingangspuffer automatisch zuweisen.

Bei der *Global-Reset*-Komponente handelt es sich um ein Signal, welches der Initialisierung des gesamten Modells bei der Inbetriebnahme dient und vom FPGA zur Verfügung gestellt wird.

Bis auf einen Prozess der Befehlschnittstelle (siehe Abschnitt 5.2), arbeiten alle Module des RCIs mit einem Systemtakt von 48 MHz.

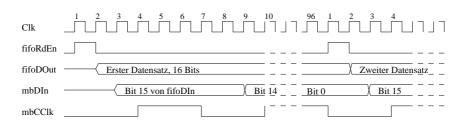

#### 5.2 RENA-Befehlsschnittstelle

Die Befehlschnittstelle *CmdInterface* ist das Bindeglied zwischen dem *RENA Control Interface* und den *RENA Module Boards*. Aus dem Systemtakt wird in diesem Modul der für den Betrieb der Boards notwendige Takt von 24 MHz erzeugt. Er wird sowohl über den Ausgangsport *busClk* auf den *RENA*-Bus übertragen als auch intern über das Signal *clk24* genutzt.

In dem CmdInterface laufen zwei voneinander unabhängige Prozesse. Der erste, der comm-Prozess, ist ein mit dem clk24 getakteter Zustandsautomat (FSM¹) der die Übermittlung der RENA-Befehle (s. Tab. 2.2) an die Boards und den Empfang ihrer Antworten übernimmt. Im Wartezustand idle überwacht die FSM den Eingang Exec. Wird auf diesem Eingang der Zustand High erkannt, wechselt sie in den Zustand tx und übermittelt den 12 Bit breiten Befehl, der am Eingang Cmd vorliegt, in drei Taktzyklen an den 4 Bit breiten RENA-Bus. Sollte es sich um einen Broadcast-Befehl handeln, kehrt die FSM sofort in den Wartezustand zurück, da die Boards diese Art von Befehlen nicht beantworten, sonst wechselt sie in den Empfangszustand.

Im Zustand rx wird bei jedem Takt der Inhalt des Busses in ein Schieberegister gespeichert. Wird nicht innerhalb von neun Taktzyklen das Bestätigungsmuster <ACK> erkannt, erstellt die FSM einen Datensatz in einem dafür vorgesehenen 51 Bit breiten Puffer, mit der Meldung des Zeitüberschreitungsfehlers. Wird der Befehl positiv quittiert, enthält der Datensatz sowohl den Befehl als auch die Antwort des Boards und die FSM geht wieder auf idle zurück. Handelt es sich um einen Auslesebefehl, geht die FSM stattdessen in den hitrx-Zustand. Der Puffer wird dabei nacheinander mit den Daten jedes empfangenen gültigen Hits beschrieben. Sollte die Eingangsleitung StoreFR auf High gesetzt sein, werden auch Forced-Reset-Hits wie normale Hits behandelt.

Sobald vom *comm*-Prozess ein Datensatz in den Puffer geschrieben wird, wird der zweite Prozess in diesem Modul aktiviert. Der *store*-Prozess läuft mit dem Systemtakt und sorgt für das korrekte Speichern der Datensätze in dem FIFO-Puffer.

Für Antworten auf *RENA*-Befehle wird nur ein Datensatz in den 16 Bit breiten FIFO geschrieben, Hits werden in vier Datensätze geteilt. Anhand des Eingangsports fifoAFull wird dem Modul mitgeteilt, dass im FIFO noch Platz für weniger als vier Datensätze zur Verfügung steht. In diesem Fall wartet der store-Prozess dass FIFO-Platz frei wird, solange bis ein neuer Hit verfügbar wird. Sollte es nicht möglich gewesen sein, den alten Hit zu speichern, wird er verworfen und eine Flagge in dem neuen Hit gesetzt, die auf diese Situation hinweist.

Dieses Modul kann wahlweise von der Kommunikationsschnittstelle oder vom Auslesesequenzer angesteuert werden, sein Verhalten bleibt in jedem Fall identisch. Durch

<sup>&</sup>lt;sup>1</sup>Finite State Machine

das Setzen des Ausgangs Busy auf High signalisiert es dem ansteuernden Modul, dass der letzte Befehl noch ausgeführt wird und keine weiteren angenommen werden.

#### 5.2.1 Erweiterung der Zeitstempel

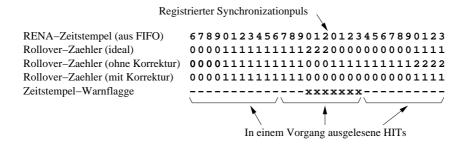

In Abschnitt 2.1.1 wurde erwähnt, dass in dem 16 Bit breiten Zähler für den Zeitstempel in den *RENA Module Boards* alle 2,18 ms ein Rollover stattfindet und dies bei niedrigen Zählraten zu Fehlern in der Messung des Zeitabstands zwischen zwei Ereignissen führen kann.

Dieses Problem wird umgangen, indem die *RENA*-Rollovers gezählt werden, diese Zahl wird dann vor den Zeitstempel gehängt. Das RCI stellt für diesen Zweck 16 solche Zähler, einen für jedes der 16 möglichen Boards, mit einer Breite von 6 Bits zur Verfügung. Der RCI-Zeitstempel weist so eine Breite von 22 Bits auf und die Zeitspanne zwischen zwei RCI-Rollover beträgt 1,398 s.

Ein RENA-Rollover wird erkannt, indem für jedes ausgelesene Board der Zeitstempel des vorletzten empfangenen Hits getrennt gespeichert wird und mit dem des letzten Hits des selben Boards verglichen wird. Ist der letzte Zeitstempel kleiner als der vorletzte, d.h. ist ihre Differenz negativ, hat sich zwischen beiden Hits ein Rollover ereignet und der Zähler wird um eins erhöht.

Um zu gewährleisten, dass es sich um maximal einen Rollover handelt, ist es wichtig, die Periode der *Forced-Reset* klein genug gegenüber 2,18 ms zu halten (s. Abschn. 2.1.1).

Solange die Zeitstempelzähler nicht während der Messung zurückgesetzt werden, liefert dieses Verfahren genaue Ergebnisse.

Beim Betrieb der RCIs mit einer externen Synchronisationsquelle kann es aber vorkommen, dass zwischen zwei aufeinanderfolgenden Auslesevorgängen derselben Boards ein Rollover und kurz danach die Synchronisation stattfinden.

Die Hits, die eventuell zwischen dem Rollover und der Synchronisation in den FIFO des Boards geschrieben werden, könnten den Rollover-Zähler einmal zuviel inkrementieren und so die gesamte Messreihe beeinträchtigen.

Im RCI wird dies verhindert indem der Rollover-Zähler beim ersten Auftreten der Negativdifferenz während des ersten Lesevorgangs nach der Synchronisation auf Null gesetzt und jedes weitere Inkrement unterdrückt wird. Alle Hits ab dem auslösenden, bis zum letzten in dem Lesevorgang werden mit einer Warnflagge versehen. Dieser Sachverhalt ist in Abbildung 5.2 veranschaulicht.

Von dieser Unsicherheit bzw. fehlerhaften Angabe des Zeitstempels können in sehr ungünstigen Fällen und bei extrem hohen Zählraten bis zu fünfzehn Hits pro Board bei jedem Synchronisationsvorgang betroffen sein.

Dieser systematische Fehler wäre von einer Auswertungssoftware leicht korrigierbar mittels eines einfachen Algorhytmus<sup>2</sup>, das für diese Entwicklungstufe nicht in der Hardware realisiert werden konnte.

### 5.3 Auslese-Sequenzer

Dieses Modul erlaubt das kontinuierliche, sequentielle Auslesen aller installierten RENA Module Boards. Auch dieses Modul ist durch eine FSM realisiert worden.

Bevor es durch Setzen des Eingangs Run auf High eingeschaltet wird, soll im Eingang MaxBrd die höchste ID-Nummer aller am Bus installierten Boards eingestellt sein.

Von der eingestellten ID aus, werden nacheinander Auslesebefehle für alle Boards an die Befehlschnittstelle gesendet. Der 12 Bit breite Befehl wird an den Ausgang intCmd gelegt und durch Setzen des Ausgangs intExec auf High freigegeben.

Vor dem Senden eines Befehls überprüft die FSM in einem Wartezustand, dass der Eingang *intBusy* auf *Low* steht, d.h. dass die Befehlschnittstelle bereit für die Ausführung von Befehlen ist.

Die Auslessequenz läuft zyklisch rückwärts, von der eingestellten ID bis Null und beginnt erneut bei dieser ID. Der Grund dafür liegt in den Eigenschaften der Vergleichslogik: das Erkennen des Wertes Null in einer Zahlvariablen wird effizienter und mit weniger Hardwareressourcen realisiert, als der direkte Vergleich zweier Zahlvariablen.

Der Zyklus wird durch eine Reihe vorbereitender *RENA*-Befehle (siehe Tabelle 2.2) eingeleitet: zuerst werden die Auslese-Flip-Flops mit MB\_WRITE\_RUNFF gesetzt, dann werden die *RENA*-FIFOs mit MB\_FIFO\_CLEAR gelöscht und die Zeitstempelzähler mit MB\_TIMER\_CLEAR zurückgesetzt.

Bei Rückkehr des Eingangs Run auf Low wird der Auslesezyklus unterbrochen und die Auslese-Flip-Flops der Boards wieder mit dem Befehl MB\_WRITE\_RUNFF zurückgesetzt.

#### 5.3.1 Synchronisation der Boards

Durch den *Handshake* mittels der *Busy*-Leitung entstehen praktisch keine Wartezeiten im Auslesebetrieb, die länger als zwei Taktzyklen des 24 MHz *RENA*-Taktes sind.

<sup>&</sup>lt;sup>2</sup>Es ist ausreichend, beim ersten markierten Hit bis zum dem vor dem zweiten Rollover, den Wert des Rollover-Zähler durch den des letzten unmarkierten Hits plus eins zu ersetzen.

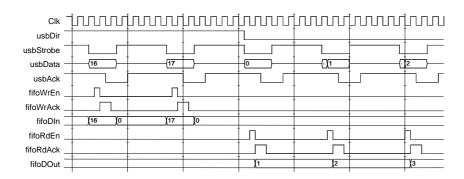

Sollen das RCI und die *RENA Module Boards* durch eine externe Taktquelle, wie z.B. durch das 1 Hz-Signal eines GPS-Empfängers synchronisiert werden, muss aus dem oben genannten Grund der Auslesezyklus rechtzeitig, wie in Abschnitt 4.1 schon erwähnt, angehalten werden.