# PMDLINK - BRIDGING THE GAP BETWEEN DPDK AND HARDWARE PACKET PROCESSING

Rubens Figueiredo<sup>1,3</sup>, Andreas Kassler<sup>2,3</sup>, Hagen Woesner<sup>1</sup>, Holger Karl<sup>4</sup>, Nic Hart<sup>1</sup>

<sup>1</sup>BISDN GmbH, <sup>2</sup>Deggendorf Institute of Technology, <sup>3</sup>Karlstad University, <sup>4</sup>Hasso-Plattner-Institute

April 4, 2025

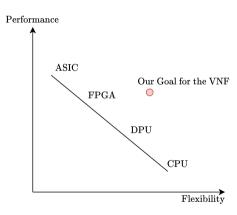

# COMMODITY HARDWARE AND PACKET PROCESSSING OFFLOADS

Software-based packet processing struggles at high speeds

## COMMODITY HARDWARE AND PACKET PROCESSSING OFFLOADS

- Software-based packet processing struggles at high speeds

- ► Hardware offload as candidate to improve performance

- Programmable ASIC

- smartNIC

- Commodity Hardware

- ► How to leverage commodity hardware NIC features to improve performance of the VNF?

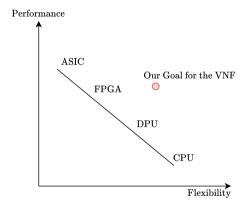

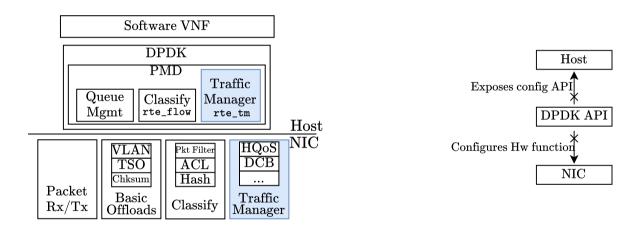

#### DPDK AS INTERFACE TO NIC

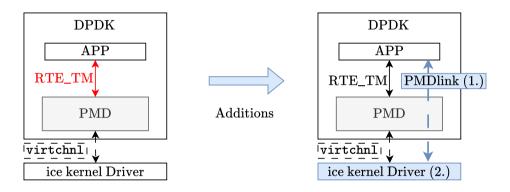

What was our issue? rte\_tm implementation of IAVF Traffic Manager is restricted

#### DPDK AS INTERFACE TO NIC

**Our approach** Direct hardware offload API through PMDlink

## Addressing the Missing Pieces

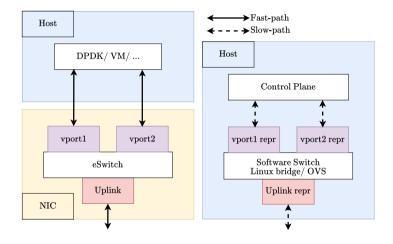

#### LEGACY AND SWITCHDEV MODES

- eSwitch: hardware component inside modern NICs

- Legacy mode: Limited offloads (MAC/ VLAN)

- Switchdev:

- Advanced offload enabled

- In Intel E810, Hierarchical QoS

Tu, William, Michal Swiatkowski, and Yossi Kuperman. "Shared Memory Pool for Representors.": https://netdevconf.info/0x18/docs/netdev-0x18-paper41-talk-paper.pdf

# ADDRESSING THE MISSING PIECES

EXTENDING DPDK AND INTEL DRIVERS

- ▶ **Problem** RTE\_TM only allows for IEEE 802.1 Qaz (ETS)¹ configuration

- **▶** Additions

- 1. Add rte\_eth\_dev\_send\_vf\_msg and similar method in IAVF driver

- 2. Modify ice kernel driver to accept HQoS messages.

<sup>&</sup>lt;sup>1</sup>Enhanced Transmission Selection: https://1.ieee802.org/dcb/802-1qaz/

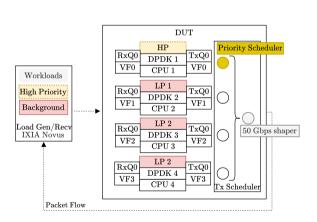

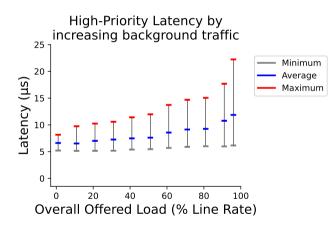

## IMPACT OF BACKGROUND TRAFFIC ON HIGH-PRIORITY LATENCY

**EXPERIMENTAL RESULTS**

How to achieve high-throughput and low latency packet processing on commodity hardware?

| Traffic Profile | Details    | Packet Size |

|-----------------|------------|-------------|

| HP              | 1 Gbps     | 178 B       |

| Background      | 10-95 Gbps | 1518 B      |

Figueiredo, Rubens, et al. "Quality of Service Performance of Multi-Core Broadband Network Gateways." 2024 8th Network Traffic Measurement and Analysis Conference (TMA). IEEE, 2024.

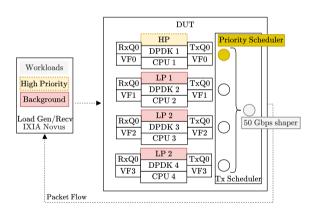

#### IMPACT OF BACKGROUND TRAFFIC ON HIGH-PRIORITY LATENCY

EXPERIMENTAL RESULTS

How to achieve high-throughput and low latency packet processing on *commodity hardware*?

**Takeaway:** SR-IOV and hardware-acceleration for fast packet processing.

Hierarchical QoS executed at hardware speeds without sacrificing flexibility.

# CHALLENGES OF HARDWARE INTEGRATION

#### **FUTURE WORK**

- ► Expressiveness of existing API implementations

- ▶ Other hardware functionality, such as header processing, parsing, matching, ...

- ► Compatibility with smartNIC, other PMD

# CONCLUSION

For Now

PMDlink as a generic API for hardware configuration

# Combining

- Flexibility of software processing, and

- ▶ Performance of hardware execution.